EUROPEAN COMMISSION SEVENTH FRAMEWORK PROGRAMME FP7-ICT-2011-C Grant agreement no.: 308830

# Deliverable D3.1

# Intermediate report for WP3: Reasoning about software/hardware interfaces

| Project acronym        | ADVENT                                               |  |

|------------------------|------------------------------------------------------|--|

| Project title          | Architecture-driven verification of systems software |  |

| Funding scheme         | FP7 FET Young Explorers                              |  |

| Scientific coordinator | Dr. Alexey Gotsman, IMDEA Software Institute,        |  |

|                        | Alexey.Gotsman@imdea.org, $+34\ 911\ 01\ 22\ 02$     |  |

## 1 Summary

Work Package 3 in the ADVENT project is concerned with reasoning about the software/hardware interfaces, and specifically with how to deal the implications of low-level hardware effects when reasoning about systems software. Through the first year of the project, we have focused on *relaxed* or *weak consistency* as the most important hardware effect that affects systems software and yet evades formal reasoning.

To enable formal reasoning about relaxed consistency, we have devised both decomposition principles (abstraction theorems) as well as program logics for verifying concurrent programs running under various weak memory consistency models, such as the TSO memory model adopted by the Sparc and x86 architectures and the C11 memory model adopted by C and C++ language standards. In more detail, we have developed:

- An *abstraction theorem for the C11 memory model* [1], which allows us to decompose the reasoning about concurrent programs into modular reasoning about each of its components. In essence, our abstraction theorem extends the definition of linearisability to the C11 setting, where executions are not longer linear event sequences.

- *Relaxed separation logic* (RSL) [15], an extension of concurrent separation logic to C11 model, allowing threads to assert ownership of part of the shared state and to transfer ownership by synchronisation operations.

- *GPS* [14], a more advanced program logic for C11 that incorporates adaptations of the three features of the more modern concurrent program logics, namely *ghost state*, *protocols*, and *separation*. GPS thus enables reasoning not only about shared state invariants, but also about its evolution over time.

- A *program logic for TSO* [7] that is designed to reason effectively about certain common synchronisation patterns that appear in TSO programs.

# 2 Motivation

In a sequential setting, the behavior of memory is simple: when a program reads a memory location, it receives the value that it wrote most recently to that location. In a concurrent setting, where the program does not define a total order on all memory accesses, however, this simple rule no longer applies. The question of what values may be yielded by reads in concurrent programs is known as the platform's *memory consistency model* (or *memory model* for short). In WP1, we identified three memory models as being of particular interest:

- (1) the x86-TSO model followed by x86 and x64 architectures,

- (2) the Power/ARM model, and

- (3) the C11 memory model adopted by the 2011 revisions of the C and C++ standards.

In this work package, we have focused mainly on the C11 memory model because it is what C/C++ programmers face and it is easily compilable to the x86-TSO and Power/ARM hardware memory models. We have developed three logics, two for reasoning about concurrent C11 the C11 memory model and one about x86-TSO. The general goal is to help programmers by providing them with reasoning principles for concurrent programs that are sound despite the rather weak consistency properties guaranteed by the memory models.

## **3** Reasoning Principles for C11 Concurrency

Library Decomposition [1] Our first contribution was to propose techniques for decomposing the reasoning about programs using concurrent libraries on the C11 memory model into separate reasoning about the libraries and their clients. (This work was done in between the submission of the project proposal and the project start, and appeared at POPL'13. We briefly described it here as it is relevant to the project.)

In more detail, we have proposed a criterion that allows to abstract a concurrent library by a simpler library serving as its specification in reasoning about the client. This criterion satisfies the *Abstraction Theorem*: if one library (a specification) abstracts another (an implementation), then the behaviours of any client using the implementation are contained in the behaviours of the client using the specification. This result allows complex library code to be replaced by simpler specifications, for verification or informal reasoning. To justify the practicality of the proposed criterion for library abstraction we have applied it two typical concurrent algorithms: a non-blocking stack and an array-based queue.

The challenge in getting such a result on the C/C++ memory model lied in soundly capturing the client-library interactions through the subtle synchronisation effects arising from the memory model. This was made only more challenging by the fact that the C11 memory model is defined axiomatically, whereas existing techniques for library abstraction, such as linearizability, have focused on operational trace-based models. To deal with this, we proposed a novel notion of a *history*, which records all interactions between a client and a library. Histories in our work consist of several partial orders on call and return actions. This is in contrast to variants of linearizability, where histories are linear sequences. We then defined an abstraction relation on histories as inclusion over partial orders, and lift this relation to give our abstraction criterion for libraries: one library abstracts another if any history of the former can be reproduced in abstracted form by the latter.

During this work, we uncovered a problem with the C11 memory model: some aspects of the model conflict with abstraction. The C11 model permits *satisfaction cycles*, where the effect of actions executed down a conditional branch is what causes the branch to be taken in the first place. This breaks the straightforward assumption that faults are confined to either client or library code: a misbehaving client can cause misbehaviour in a library, which can in turn cause the original client misbehaviour! For these reasons, we actually defined *two* distinct library abstraction criteria: one for general C11, and one for a language without the feature leading to satisfaction cycles. The former requires an a priori check that the client and the library do not access each others' internal memory locations, which hinders compositionality. The latter lifts this restriction (albeit for a C11 model modified to admit incomplete program runs) and thus provides evidence that satisfaction cycles are to blame for non-compositional behaviour. Our results have motivated an ongoing effort to revise the memory model:

#### http://www.open-std.org/jtc1/sc22/wg21/docs/papers/2013/n3710.html

**Relaxed separation logic (RSL)** [15] While having developed decomposition principles is clearly a very useful step for reasoning about complex software, we also need to have techniques for verifying the individual components with respect to their specifications. To achieve this, we have developed two program logics for C11 concurrency, RSL and GPS.

The goal of relaxed separation logic (RSL) was to show that C11 concurrency supports resource reasoning in the style of concurrent separation logic (CSL) [11], and that proofs written in CSL can easily be adapted to work under weaker consistency guarantees.

Specifically, we focused on the various different kinds of memory accesses supported by C11: nonatomic, relaxed atomic, acquire atomic, release atomic, and sequentially consistent (SC) atomic, each of which provides different consistency guarantees, and has different implementation costs. On the one end of the spectrum, races on non-atomic accesses result in completely undefined behaviour (they are treated as programming errors); on the other end, SC-atomic accesses are globally synchronized. The implementation cost and the guarantees provided by relaxed, acquire, and release accesses lie somewhere in between: different threads can observe them happening in different orders, but fewer or no memory fences are needed (depending on the architecture).

What we managed to show with RSL, is that ownership-based reasoning is sound, and moreover that ownership can be transferred along acquire/release atomic memory accesses and does not require the more expensive SC-accesses.

In more detail, RSL follows the resourceful reading of separation logic triples. As in standard separation logic, when we assert the Hoare triple  $\{P\} \ C \ \{Q\}$ , we say that the command C will not access any memory other than that given by its precondition, P, or subsequently acquired during its execution. We thus support the parallel composition rule of separation logic,

$$\frac{\{P_1\} C_1 \{Q_1\} \{P_2\} C_2 \{Q_2\}}{\{P_1 * P_2\} C_1 \| C_2 \{Q_1 * Q_2\}}$$

(PAR)

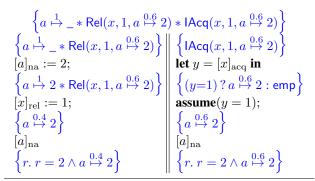

which ensures that the two threads do not have any races on nonatomic memory accesses, a condition required by C11. To handle acquire/release atomics, we introduce two new assertion kinds,  $\operatorname{Rel}(\ell, Q_1)$  and  $\operatorname{Acq}(\ell, Q_2)$ . These denote respectively the permissions to perform a release-write of some value v at location  $\ell$  and give away ownership of the resource described by  $Q_1(v)$ , or an acquire-read and gain ownership of  $Q_2(v)$ . With these assertion forms we provide simple proof rules for release writes and acquire reads, similar to those for releasing and acquiring mutual exclusion locks in CSL.

The main challenge in this work was to prove the soundness of the program logic, as there were two really significant obstacles we had to overcome.

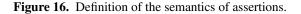

- 1. No global notions of state and time: Traditionally,  $\{P\} C \{Q\}$  asserts that if we execute C in an initial state satisfying P and it terminates, then the final state will satisfy Q. In C11 concurrency, however, the terms "initial state" and "final state" are ill-defined, because there exist no global notions of time or state. To interpret triples, we thus resorted to *logical* local notions of time and state. We defined a logical notion of local state at each event of a program execution, and thread the logical state through C11 "happens-before" edges.

- 2. No operational semantics: Concurrent program logics are typically proved sound over an operational or a trace semantics. In either case, the meaning of Hoare triples can be defined in terms of an auxiliary predicate by induction over the length of an execution trace. These definitions cannot directly be extended to the C11 axiomatic model as there is no obvious total order for the induction. Our solution was to order the C11 events according to the total number of events that happen before them.

The paper introducing RSL was published at OOPSLA 2013 [15] and is attached. We are currently working on extensions of RSL to handle memory barriers.

**GPS** [14] Our next contribution was *GPS*, a more advanced program logic for C11 concurrency, published as a MPI-SWS technical report. A slightly updated version of the technical report is currently under submission to OOPSLA 2014.

Generally, the goal of most program logics is to prove "deep" correctness properties of code, and to do so in a *modular* fashion, whereby different components of a program can be verified in isolation, given only logical specifications of the other components. Modern logics for SC concurrency meet this goal through a variety of mechanisms—among the most widespread and effective are the following:

- Ownership and separation. Concurrent programs are often inherently modular in the sense that different threads within a program control (or "own") disjoint pieces of the program state. This modularity is important for simplifying verification: if a thread owns a piece of state, one should be able to verify the thread's manipulations of that state without worrying about interference from other threads. Modern logics encapsulate this kind of reasoning through the mechanisms of ownership and separation.

- *Protocols.* Separation lets one dispense with interference implicitly when threads do not in fact interfere. But sometimes explicit reasoning about interference is unavoidable, e.g., when reasoning about racy (lock-free) data structures. In such cases, the most basic mechanism for restoring modular reasoning is the *invariant*, which describes a property holding of a piece of shared state at all times. With an invariant installed, different threads can be verified modularly so long as they all respect the invariant.

More generally, since invariants can be overly restrictive, modern logics support various forms of *protocols* for legislating interference. The best-known protocol mechanism is *rely-guarantee* [8], which describes the state transitions a thread may perform (the guarantee) vs. those its environment may perform (the rely). Recent protocol mechanisms improve upon rely-guarantee by supporting more abstract/concise forms of shared state transition systems [13].

• *Ghost state*. Last but not least, *ghost* (or auxiliary) state refers generally to any behaviorpreserving instrumentation of a program (or its proof) with additional "logical" state for the purposes of verification. Ghost state is often used to expose control flow, or to summarize execution history, in a way that could not be done just in terms of the "physical" state manipulated by the program. Furthermore, it is essential for the completeness of basic concurrency logics.

In newer logics, ghost state, protocols, and separation are used in tandem to great effect. For example, ghost state can be used to encode logical "permissions" (or "tokens"), which are ownable resources that control the ability to make certain transitions in shared state protocols. Ownership of permissions can then be transferred back and forth between threads *via* the same shared protocols, in turn providing a way to model the dynamic "role-playing" that occurs in realistic concurrent code. Logics such as RGSep [16], LRG [6], Deny-Guarantee [5], VCC [2], Chalice [9], CAP [4], CaReSL [13], FCSL [10], iCAP [12], and TaDA [3] depend on such a synthesis of ghost state, protocols, and separation.

While the aforementioned mechanisms provide powerful, modular reasoning about concurrency, there are serious obstacles to adapting them to weak memory models. Besides those mentioned in the section about RSL, we also have:

- *Protocol obstacles.* Most logics support protocols that govern multiple memory locations simultaneously, connecting the value of one location to another. But even this simple mechanism is unsound for weak memory: updates to different locations may appear in contradictory orders to different threads, so a thread can appear to be following the protocol from its own point of view while violating it from the point of view of other threads.

- *Ghost state obstacles.* Traditional ghost state is incorporated by introducing explicit reads and writes to a program text, with the constraint that these operations must not change the code's observable behavior. But in weak memory models it is not clear how to usefully incorporate such reads and writes without also introducing events and ordering into the event graph that ultimately affect the program's behavior.

GPS is the first logic that properly supports ghost state, protocols and separation in a weak memory setting. GPS builds on the groundwork laid by RSL, extending it as follows:

- Protocols. GPS supports per-location (PL) protocols, which are modeled after the protocols in recent concurrency logics but restricted in order to be sound under weak memory. The key to regaining soundness is to insist that a protocol may only precisely dictate the evolution of a single shared memory location, although it may make bounded assertions about the state of other memory locations, e.g., "x's value may only grow over time, and when x contains n, y must contain at least n as well."

- *Ghost state*. The states of PL-protocols already constitute a useful form of ghost state for summarizing, e.g., the history of an execution. To support ownable logical resources (e.g., permissions), GPS offers an additional facility called *ghosts*. Ghosts enable one to create and manipulate whatever kind of logical resource one needs for a particular verification, so long as it can be formulated as a partial commutative monoid.

As with RSL, the entire logic, model and soundness proof of GPS have been formalized in Coq and are available online.

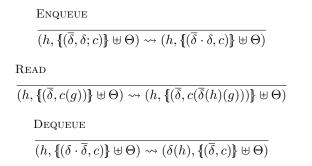

### 4 Reasoning Principles for x86-TSO

Besides reasoning about the C11 memory model, we have also developed a program logic for reasoning about concurrent programs running under the TSO memory model. We have extended separation logic with a notion of *TSO spaces*. TSO spaces are similar to the shared resources of Concurrent Separation Logic (CSL) [11], except that memory owned by a TSO space may be accessed directly via TSO operations (memory accesses with TSO semantics) rather than using classical critical sections. Also, where CSL associates a resource invariant with each resource, we associate an *abstract state space* with each TSO space, as well as an *abstraction predicate* that associates each abstract state with a corresponding separation logic formula. The abstract state space is equipped with an *abstract reachability* pre-order  $\leq$ .

Knowledge about the state of a TSO space in the proof of a thread is represented as an abstract state, representing the thread's view of the state of the TSO space. A thread's view is a lower bound (under the abstract reachability pre-order) on the actual state of the TSO space.

Each TSO write operation is associated with an *abstract state transition function*, mapping an abstract pre-state to an abstract post-state. These abstract state transition functions must respect the abstract reachability relation and properly abstract the concrete behavior of the TSO operation. Also, crucially, to account for TSO's relaxed behavior, the abstract state transition functions must be *monotonic*: they must respect reachability and be sound with respect to concrete behavior not only in the current abstract state, but also in all reachable future abstract states. In a thread's proof, when the thread performs a TSO write operation, its local view of the TSO space is updated per the abstract state transition function.

Each TSO read operation is associated with a function, f, mapping result values to new abstract states. This function must satisfy the property that for any result value, v, and for any future abstract state,  $\alpha'$ , if the target location may have value v in this abstract state, then  $f(v) \leq \alpha'$ . In a thread's proof, when the thread performs a TSO read operation, its local view of the TSO space is replaced with the (hopefully more precise) lower bound given by function f.

For example, consider an implementation of a Java virtual machine, where field accesses are implemented as TSO operations. Threads may create objects and leak references to those objects to other threads without synchronization. The VM implementation must ensure nonetheless that each thread only sees objects with properly initialized run-time type information (such as the pointer to the virtual method dispatch table).

To verify such a JVM implementation using the proposed logic, we put the heap in a TSO space. As the abstract state space, we adopt the powerset of addresses in this heap, each state representing the set of the addresses of the currently allocated and initialized objects.

The subset relation serves as the reachability order. The abstraction predicate states (1) that allocated objects occupy disjoint heap space, (2) that they properly point to an existing virtual method dispatch table, and (3) that their fields point to allocated objects. Each thread is aware of the addresses of objects it allocated itself, as well as addresses read from fields of known objects. That is, reading a field updates the thread's view by inserting the newly discovered object address into the abstract state. After a thread allocates an object and initializes its run-time type information, it performs a no-op operation on the TSO space to update its local view of the set of allocated objects, inserting the newly allocated object into the abstract state. Writing the value of a local variable to a field corresponds to the identity function at the abstract level, since all object references a thread holds in local variables are already in the thread's local view.

The approach is described in more detail in [7]. Besides a definition and soundness argument of the approach, this document also reports on a preliminary encoding of this approach into the logic of the VeriFast program verifier, and on three example proofs: an example that captures the virtual machine scenario, a lock implementation, and a producer-consumer example.

### References

- M. Batty, M. Dodds, and A. Gotsman. Library abstraction for C/C++ concurrency. In POPL, pages 235–248. ACM, 2013.

- [2] E. Cohen, M. Dahlweid, M. A. Hillebrand, D. Leinenbach, M. Moskal, T. Santen, W. Schulte, and S. Tobies. VCC: A practical system for verifying concurrent C. In *TPHOLs*, volume 5674 of *LNCS*, pages 23–42. Springer, 2009.

- [3] P. da Rocha Pinto, T. Dinsdale-Young, and P. Gardner. TaDA: A logic for time and data abstraction. In *ECOOP*, 2014.

- [4] T. Dinsdale-Young, M. Dodds, P. Gardner, M. Parkinson, and V. Vafeiadis. Concurrent abstract predicates. In ECOOP, 2010.

- [5] M. Dodds, X. Feng, M. Parkinson, and V. Vafeiadis. Deny-guarantee reasoning. In ESOP, 2009.

- [6] X. Feng. Local rely-guarantee reasoning. In POPL, 2009.

- [7] B. Jacobs. Verifying TSO programs. Technical Report CW-660, Department of Computer Science, KU Leuven, 2014.

- [8] C. B. Jones. Specification and design of (parallel) programs. In IFIP Congress, 1983.

- [9] K. R. M. Leino, P. Müller, and J. Smans. Verification of concurrent programs with Chalice. In FOSAD, volume 5705 of LNCS, pages 195–222. Springer, 2009.

- [10] A. Nanevski, R. Ley-Wild, I. Sergey, and G. A. Delbianco. Communicating state transition systems for fine-grained concurrent resources. In ESOP, 2014.

- [11] P. O'Hearn. Resources, concurrency and local reasoning. TCS, 2007.

- [12] K. Svendsen and L. Birkedal. Impredicative concurrent abstract predicates. In ESOP, 2014.

- [13] A. Turon, D. Dreyer, and L. Birkedal. Unifying refinement and Hoare-style reasoning in a logic for higher-order concurrency. In *ICFP*, pages 377–390. ACM, 2013.

- [14] A. Turon, V. Vafeiadis, and D. Dreyer. GPS: Navigating weak memory with ghosts, protocols, and separation. Technical Report MPI-SWS-2014-004, MPI-SWS, 2014.

- [15] V. Vafeiadis and C. Narayan. Relaxed separation logic: a program logic for c11 concurrency. In OOPSLA, pages 867–884, 2013.

- [16] V. Vafeiadis and M. Parkinson. A marriage of rely/guarantee and separation logic. In CONCUR, 2007.

## List of Attached Papers

- [15] Viktor Vafeiadis and Chinmay Narayan. Relaxed separation logic: a program logic for c11 concurrency. In OOPSLA'13, pages 867–884. ACM 2013.

- [14] Aaron Turon, Viktor Vafeiadis, and Derek Dreyer. GPS: Navigating weak memory with ghosts, protocols, and separation. Technical Report MPI-SWS-2014-004, MPI-SWS, 2014.

- [7] Bart Jacobs. Verifying TSO programs. Technical Report CW-660, Department of Computer Science, KU Leuven, 2014.

# Relaxed Separation Logic: A Program Logic for C11 Concurrency

Viktor Vafeiadis

Max Planck Institute for Software Systems (MPI-SWS) viktor@mpi-sws.org

#### Abstract

We introduce *relaxed separation logic* (RSL), the first program logic for reasoning about concurrent programs running under the C11 relaxed memory model. From a user's perspective, RSL is an extension of concurrent separation logic (CSL) with proof rules for the various kinds of C11 atomic accesses. As in CSL, individual threads are allowed to access non-atomically only the memory that they own, thus preventing data races. Ownership can, however, be transferred via certain atomic accesses. For SC-atomic accesses, we permit arbitrary ownership transfer; for acquire/release atomic accesses, we allow ownership transfer only in one direction; whereas for relaxed atomic accesses, we rule out ownership transfer completely. We illustrate RSL with a few simple examples and prove its soundness directly over the axiomatic C11 weak memory model.

*Categories and Subject Descriptors* D.3.1 [*Programming Languages*]: Formal Definitions and Theory; F.3.1 [*Logics and Meanings of Programs*]: Specifying and Verifying and Reasoning about Programs

*Keywords* Concurrency; Weak memory models; C/C++; Proof system; Separation logic

#### 1. Introduction

Wanting to enable many hardware and software optimizations, modern programming language definitions provide rather weak guarantees on the semantics of concurrent memory accesses allowing, for example, different threads to observe shared operations happening in different orders. One such case is the concurrency model adopted by the 2011 revisions of the C and C++ standards (ISO/IEC 9899:2011;

OOPSLA '13, October 29–31, 2013, Indianapolis, Indiana, USA.

Copyright is held by the owner/author(s). Publication rights licensed to ACM. ACM 978-1-4503-2374-1/13/10...\$15.00.

http://dx.doi.org/10.1145/2509136.2509532

Chinmay Narayan

Indian Institute of Technology, Delhi chinmay@cse.iitd.ac.in

ISO/IEC 14882:2011), which we will study in this paper and refer to as the C11 model.

C11 provides several kinds of memory accesses—nonatomic, relaxed atomic, acquire atomic, release atomic, and sequentially consistent (SC) atomic—each providing different consistency guarantees. On the one end of the spectrum, races on non-atomic accesses result in completely undefined behaviour (they are treated as programming errors); on the other end, SC-atomic accesses are globally synchronized. The guarantees provided by relaxed, acquire, and release accesses lie somewhere in between: different threads can observe them happening in different orders.

The reason for having all these kinds of accesses is that they map differently to the various common architectures, and have very different implementation costs. Non-atomic and relaxed atomic accesses are generally rather cheap as they correspond to vanilla machine loads and stores, and may be reordered by the compiler and/or by an out-of-order execution unit. At the other end of the spectrum, SC accesses are very expensive because their implementation involves a full memory barrier. The cost of acquire and release accesses depends a lot on the architecture. On x86, they are compiled down to plain reads and writes (Batty et al. 2011) and are therefore cheap. On PowerPC and ARM, the cost is somewhat higher as they induce a memory barrier, but of a weaker kind than full memory barriers (Sarkar et al. 2012).

Our goal is to help C11 programmers by providing them with sound reasoning principles for concurrent programs. We show that C11 concurrency supports resource reasoning in the style of separation logic (O'Hearn 2007); in particular, ownership can be transferred along acquire/release atomic memory accesses and does not require SC-accesses.

We develop *relaxed separation logic* (RSL), a program logic that follows the resourceful reading of separation logic triples. When we assert the Hoare triple  $\{P\}$  Cmd  $\{Q\}$ , we say that the command Cmd will not access any memory other than that given by its precondition, P, or subsequently acquired during its execution. We thus support the parallel composition rule of separation logic,

$$\frac{\{P_1\} Cmd_1 \{Q_1\} \{P_2\} Cmd_2 \{Q_2\}}{\{P_1 * P_2\} Cmd_1 \| Cmd_2 \{Q_1 * Q_2\}}$$

(PAR)

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

which ensures that the two threads do not have any races on non-atomic memory accesses, a condition required by C11.

To handle acquire/release atomics, we introduce two new assertion kinds,  $\text{Rel}(\ell, Q_1)$  and  $\text{Acq}(\ell, Q_2)$ . These denote respectively the permissions to perform a release-write of some value v at location  $\ell$  and give away ownership of the resource described by  $Q_1(v)$ , or an acquire-read and gain ownership of  $Q_2(v)$ . With these assertion forms we provide simple proof rules for release writes and acquire reads, similar to those for releasing and acquiring mutual exclusion locks in concurrent separation logic.

Besides RSL itself, the main contribution of this work was to define the meaning of Hoare triples in a relaxed memory model setting, so as to prove the soundness of RSL. This was rather challenging for three main reasons.

No global state/time: Traditionally,  $\{P\}$  Cmd  $\{Q\}$  asserts that if we execute Cmd in an initial state satisfying P and it terminates, then the final state will satisfy Q. In C11 concurrency, however, the terms "initial state" and "final state" are ill-defined, because there exist no global notions of time or state.

To interpret triples, we thus resort to *logical* local notions of time and state. We define a logical notion of local state at each event of a program execution, and thread the logical state through C11 "happens-before" edges.

- Assertions in heaps: Our assertions for dealing with acquire and release atomics require that the logical heaps used to interpret them contain assertions. This results in a circularity in the model of assertions, which for simplicity we resolve by storing syntactic assertions.

- No operational semantics: Concurrent program logics are typically proved sound over an operational or a trace semantics. In either case, the meaning of Hoare triples can be defined in terms of an auxiliary predicate by induction over the length of an execution trace. These definitions cannot directly be extended to the C11 model as there is no obvious total order for the induction. Our solution is to order the C11 events according to the total number of events that happen before them.

As a secondary contribution, we observed that the semantics of relaxed atomic memory accesses in C11 is too weak to permit even the most basic reasoning principles about them, which in turn renders basic compiler optimizations unsound. In order to allow such reasoning principles, we proposed a crude fix to C11, which we discuss in Section 6.

In the remainder of this paper, we define a minimal concurrent programming language (§2), review the C11 concurrency model (§3), describe the assertions and proofs rules of RSL (§4), verify a few examples using RSL (§5), explain the problems caused by relaxed accesses and their resolution (§6), present the semantics of assertions and Hoare triples and sketch the main parts of the soundness proof (§7). We conclude with a discussion of related and future work (§8). A Coq formalization of the soundness proof of RSL can be found at the following URL.

http://www.mpi-sws.org/~viktor/rsl/

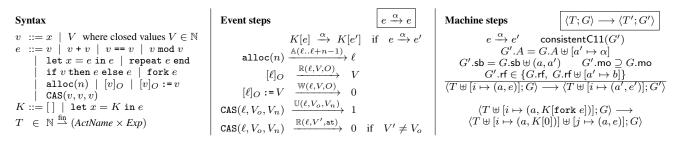

#### 2. Programming Language

In order to focus on the concurrency aspects of C11 and to avoid the inherent complexity of a large language like C, we introduce a minimal concurrent programming language featuring the various kinds of memory accesses supported by C11. Following Batty et al. (2012), we omit consume reads from the model, because they are relevant only for a few architectures (PowerPC and ARM) and substantially complicate the model. For simplicity, we also omit memory fences.

To make the local sequential execution order explicit, we present the grammar of expressions in A-normal form (cf. Flanagan et al. 1993). Atomic expressions,  $e \in AExp$ , consist of variables and values (locations and numbers). Program expressions,  $E \in Exp$ , consist of atomic expressions, let-bound computations, conditionals, loops, parallel composition, memory allocation, loads, stores, and atomic compare-and-swap (**CAS**) instructions.

$$\begin{array}{ll} v \in \mathsf{Val} ::= \ell \mid n & \text{where } \ell \in \mathsf{Loc}, n \in \mathbb{N} \\ e \in \mathsf{AExp} ::= x \mid v & \text{where } x \in \mathsf{Var} \\ E \in \mathsf{Exp} ::= e \mid \mathsf{let} \; x = E \; \mathsf{in} \; E' \mid \mathsf{if} \; e \; \mathsf{then} \; E \; \mathsf{else} \; E' \\ \mid \mathsf{repeat} \; E \; \mathsf{end} \mid E_1 \| E_2 \mid \mathsf{alloc}() \\ \mid [e]_X \mid [e]_Y := e' \mid \mathbf{CAS}_{Z,W}(e, e', e'') \end{array}$$

where  $X \in \{\text{sc, acq, rlx, na}\}, Y \in \{\text{sc, rel, rlx, na}\}, Z \in \{\text{sc, rel_acq, acq, rel, rlx}\}, W \in \{\text{sc, acq, rlx}\}$

As in C, in conditional expressions we treat zero as false and non-zero values as true. The construct repeat E end executes E repeatedly until it returns a non-zero value.

Memory accesses are annotated by their mode: sequentially consistent (sc), acquire (acq), release (rel), combined release-acquire (rel\_acq), relaxed (rlx), or non-atomic (na). According to the C standard, not all modes are available for all accesses: reads cannot be releases, writes cannot be acquires, **CAS**s cannot be non-atomic. These restrictions are to avoid redundancy in the language. For example, an acquire write, if such a thing were allowed, would behave exactly the same as a relaxed write.

**CAS** is an atomic operation used to heavily in lock-free concurrent algorithms. It takes a location,  $\ell$ , and two values, v' and v'', as arguments. It atomically checks if the value at location is v' or not. If the value is same as v', then **CAS** succeeds: it atomically writes v'' to  $\ell$  and returns the old value. If the value is different, **CAS** fails: it returns that value and does not modify the location. **CAS** is annotated with two access modes: one to be used for the successful case, and one for the unsuccessful case.

For conciseness in examples, we will often write expressions such as  $[E]_{na}$  instead of let x = E in  $[x]_{na}$ . We also write  $E_1$ ;  $E_2$  instead of let  $x = E_1$  in  $E_2$  when  $x \notin fv(E_2)$ .

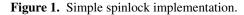

$$\begin{split} new\_lock() &= \mathbf{let} \; x = \mathbf{alloc}() \; \mathbf{in} \; [x]_{\mathrm{rel}} := 1; x \\ spin(x) &= \mathbf{repeat} \; [x]_{\mathrm{rlx}} \; \mathbf{end} \\ lock(x) &= \mathbf{repeat} \; spin(x); \mathbf{CAS}_{\mathrm{acq,rlx}}(x, 1, 0) \; \mathbf{end} \\ unlock(x) &= \; [x]_{\mathrm{rel}} := 1 \end{split}$$

**Spinlock Example** There are two important uses of acquire/release accesses: in implementing locks, and in message passing. Relaxed accesses are useful in cases of optimistic reads, where the value read, if it is of interest to the algorithm, will be read again by an acquire read, or an acquire fence will be issued. For example, in the simple CASbased spinlock implementation shown in Figure 1, lock(x)performs an acquire-on-success CAS and unlock(x) does a release write. The optimistic spin(x) loop that waits for the lock to become free, in contrast, does relaxed reads. The combined release-acquire CAS is supposed to be used for operations that atomically release one lock and acquire another—this is possible, for example, if the locks are represented as different bits of the same word. Further examples can be found in McKenney and Garst (2011).

#### 3. The C11 Memory Model

The C11 memory model is defined axiomatically in terms of program executions. A program *execution* consists of a set of actions and several binary relations over them. Actions describe the memory operations performed by the program, and are labelled with information about the memory order of the operation, the address accessed and the values read and/or written.

$$\begin{array}{l} \mathsf{Act} ::= \mathrm{skip} \mid \mathsf{W}_{(\mathrm{sc}|\mathrm{rel}|\mathrm{rlx}|\mathrm{na})}(\ell, v) \mid \mathsf{R}_{(\mathrm{sc}|\mathrm{acq}|\mathrm{rlx}|\mathrm{na})}(\ell, v) \\ \mid \mathsf{RMW}_{(\mathrm{sc}|\mathrm{rel}_{-}\mathrm{acq}|\mathrm{acq}|\mathrm{rel}|\mathrm{rlx})}(\ell, v, v') \mid \mathsf{A}(\ell) \end{array}$$

In summary, we have a no-op action; SC, release, relaxed and non-atomic writes; SC, acquire, relaxed, and non-atomic reads; atomic read-modify-write actions; and allocations. The no-op (skip) action represents local computations, thread forks and joins.

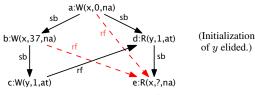

For the subset of C11 we consider, an execution contains the following relations:<sup>1</sup>

- Sequenced-before (sb) relates actions of the same thread that follow one another in control flow. We have sb(a, b) if a and b belong to the same thread and a *immediately* precedes b in the thread's control flow, or a is a fork action and b the first action of the forked thread, or b is a join action and a the last action of the joined thread.

- The *reads-from* map (rf) maps every read action r to the write action w that wrote the value read by r.

- The *memory-order* relation (mo) is a total order on the store actions writing to the same atomic location.

- The *sequential-consistency* order (sc) is a total order over all SC-atomic actions.

Formally, let AName be a countably infinite of action names. Then, an execution,  $\mathcal{X}$ , is represented as a tuple,  $\langle \mathcal{A}, \mathsf{lab}, \mathsf{sb}, \mathsf{rf}, \mathsf{mo}, \mathsf{sc} \rangle$ , where  $\mathcal{A} \subseteq_{\mathrm{fin}}$  AName is the set of action names included in the execution,  $\mathsf{lab} \in \mathcal{A} \to \mathsf{Act}$  maps every action identifier to its label,  $\mathsf{rf} \in \mathcal{A} \rightharpoonup \mathcal{A}$  is the reads-from map, and sb, mo,  $\mathsf{sc} \in \mathcal{P}(\mathcal{A} \times \mathcal{A})$  are the sequenced-before relation, the memory order, and the sequential consistency order respectively.

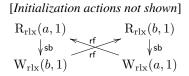

From these relations, C11 defines a number of derived relations, the most important of which are: the *synchronizes-with* relation and the *happens-before* order.

- *Synchronizes-with* (sw) relates acquire reads with the release writes that precede in mo order the write whose value was read by the acquire read provided that all the writes between these two writes belong to the same thread or are RMW operations.

- *Happens-before* (hb) is a partial order on actions formalizing the intuition that one action was completed before the other. In the C11 subset we consider, hb = (sb∪sw)<sup>+</sup>.

The semantics of a program is given by the set of *consistent* executions. An execution is said to be consistent if it satisfies the axioms of the memory model, which will be presented shortly. If, however, any of these consistent executions contains a data race on non-atomic actions, i.e. events generated from two conflicting operations on the same non-atomic location not ordered by hb in either direction, then the program is deemed to have arbitrary semantics. Thus, any sound program logic for C11 concurrency must ensure its specifications imply race-freedom for non-atomic actions.

*Expression Semantics* Let CExp denote closed expressions (i.e., ones with no free variables). The semantics of such closed expressions,  $[\![E]\!]$ , is given in Figure 2 as a set of tuples  $\langle res, \mathcal{A}, lab, sb, fst, lst \rangle$ . These tuples represent finite complete executions as well as finite incomplete execution prefixes (used to model infinite executions), where:

- (1) res is the result of evaluating the expression or  $\perp$  if the execution is incomplete;

- (2) A is the set of all actions contained in the execution;

- (3) lab labels the actions with the corresponding operations;

- (4) sb represents the sequenced-before relation; and

(5) fst and lst are the first and last actions in the sb-order. For uniformity, we record the last action even in incomplete executions. In the parallel composition case, the auxiliary function combine( $res_1, res_2$ ) returns  $res_1$  if  $res_2 \neq \bot$  and  $\bot$  otherwise. In the [[E]] semantics, allocations can return an arbitrary new location, and reads can read an arbitrary value. These will later be constrained by the consistency axioms.

<sup>&</sup>lt;sup>1</sup> The full model includes two additional relations, dd (data dependency) and dob (dependency ordered before), used to define the happens-before relation for consume reads.

$$\begin{bmatrix} - \end{bmatrix} : \operatorname{CExp} \to \mathbb{P}(\langle \operatorname{res} : \operatorname{Val} \cup \{\bot\}, \mathcal{A} : \mathbb{P}(\operatorname{AName}), \operatorname{lab} : \mathcal{A} \to \operatorname{Act}, \operatorname{sb} : \mathbb{P}(\mathcal{A} \times \mathcal{A}), fst : \mathcal{A}, lst : \mathcal{A} \rangle) \\ \begin{bmatrix} v \end{bmatrix} \stackrel{def}{=} \{\langle v, \{a\}, \operatorname{lab}, \emptyset, a, a \rangle \mid a \in \operatorname{AName} \wedge \operatorname{lab}(a) = \operatorname{skip} \} \\ \begin{bmatrix} \operatorname{lalloc}() \end{bmatrix} \stackrel{def}{=} \{\langle v, \{a\}, \operatorname{lab}, \emptyset, a, a \rangle \mid a \in \operatorname{AName} \wedge \ell \in \operatorname{Loc} \wedge \operatorname{lab}(a) = \operatorname{A}(\ell) \} \\ \begin{bmatrix} [v]_Z : = v'] \stackrel{def}{=} \{\langle v', \{a\}, \operatorname{lab}, \emptyset, a, a \rangle \mid a \in \operatorname{AName} \wedge \operatorname{lab}(a) = \operatorname{W}_Z(v, v') \} \\ \\ \begin{bmatrix} [v]_Z \end{bmatrix} \stackrel{def}{=} \{\langle v', \{a\}, \operatorname{lab}, \emptyset, a, a \rangle \mid a \in \operatorname{AName} \wedge v' \in \operatorname{Val} \wedge \operatorname{lab}(a) = \operatorname{R}_Z(v, v') \} \\ \\ \cup \{ \langle v, \{a\}, \operatorname{lab}, \emptyset, a, a \rangle \mid a \in \operatorname{AName} \wedge v' \in \operatorname{Val} \wedge v' \neq v_o \wedge \operatorname{lab}(a) = \operatorname{R}_Y(v, v') \} \\ \\ \cup \{ \langle v_o, \{a\}, \operatorname{lab}, \emptyset, a, a \rangle \mid a \in \operatorname{AName} \wedge \operatorname{lab}(a) = \operatorname{RMW}_X(v, v_o, v_n) \} \\ \\ \begin{bmatrix} \operatorname{let} x = E_1 \operatorname{in} E_2 \end{bmatrix} \stackrel{def}{=} \{\langle \bot, \mathcal{A}_1, \operatorname{lab}_1, \operatorname{sb}_1, fst_1, \operatorname{lst}_1 \rangle \mid \langle \bot, \mathcal{A}_1, \operatorname{lab}_1, \operatorname{sb}_1, fst_1, \operatorname{lst}_2 \rangle \mid \\ \langle v_1, \mathcal{A}_1, \operatorname{lab}_1, \operatorname{sb}_1, fst_1, \operatorname{lst}_1 \rangle \in [\mathbb{L}_1] \wedge \langle \operatorname{res}_2, \mathcal{A}_2, \operatorname{lab}_2, \operatorname{lab}_2, \operatorname{lab}_2, \operatorname{lab}_2, \operatorname{lab}_2, \operatorname{lab}_2, \operatorname{lab}_2, \operatorname{lab}_2, \operatorname{lab}_3, \operatorname{lab}_3, \operatorname{lab}_4, \operatorname{$$

$\mathsf{totalorder}(\{a \in \mathcal{A} \mid \mathsf{isSeqCst}(a)\}, \mathsf{sc}) \land \mathsf{hb}_{\mathsf{SeqCst}} \subseteq \mathsf{sc} \land \mathsf{mo}_{\mathsf{SeqCst}} \subseteq \mathsf{sc}$ (ConsistentSC)  $\forall b. \ \mathsf{rf}(b) \neq \bot \iff \exists \ell, a. \ \mathsf{iswrite}_{\ell}(a) \land \mathsf{isread}_{\ell}(b) \land \mathsf{hb}(a, b)$ (ConsistentRFdom)  $\forall a, b. \ \mathsf{rf}(b) = a \implies \exists \ell, v. \ \mathsf{iswrite}_{\ell, v}(a) \land \mathsf{isread}_{\ell, v}(b) \land \neg \mathsf{hb}(b, a)$ (ConsistentRF)  $\forall a, b. \ \mathsf{rf}(b) = a \land (\mathsf{mode}(a) = \mathrm{na} \lor \mathsf{mode}(b) = \mathrm{na}) \implies \mathsf{hb}(a, b)$ (ConsistentRFna)  $\forall a, b. \ \mathsf{rf}(b) = a \land \mathsf{isSeqCst}(b) \implies \mathsf{isc}(a, b) \lor \neg \mathsf{isSeqCst}(a) \land (\forall x. \mathsf{isc}(x, b) \Rightarrow \neg \mathsf{hb}(a, x))$ (RestrSCReads)  $\nexists a, b.$  hb $(a, b) \land mo(rf(b), rf(a)) \land locs(a) = locs(b)$ (CoherentRR)  $\nexists a, b.$  hb $(a, b) \land mo(rf(b), a) \land iswrite(a) \land locs(a) = locs(b)$ (CoherentWR)  $\nexists a, b.$  hb $(a, b) \land mo(b, rf(a)) \land iswrite(b) \land locs(a) = locs(b)$ (CoherentRW)  $\forall a. \text{ isrmw}(a) \land \mathsf{rf}(a) \neq \bot \implies \mathsf{mo}(\mathsf{rf}(a), a) \land \nexists c. \mathsf{mo}(\mathsf{rf}(a), c) \land \mathsf{mo}(c, a)$ (AtomicRMW)  $\forall a, b, \ell. \ \mathsf{lab}(a) = \mathsf{lab}(b) = \mathcal{A}(\ell) \implies a = b$ (ConsistentAlloc) where  $\mathsf{iswrite}_{\ell,v}(a) \stackrel{\text{def}}{=} \exists X, v_{\text{old}}. \mathsf{lab}(a) \in \{W_X(\ell, v), \mathrm{RMW}_X(\ell, v_{\text{old}}, v)\}$  $\mathsf{iswrite}_{\ell}(a) \stackrel{\text{def}}{=} \exists v. \mathsf{iswrite}_{\ell,v}(a)$  $\mathsf{isread}_{\ell,v}(a) \stackrel{\text{def}}{=} \exists X, v_{\text{new}}. \mathsf{lab}(a) \in \{\mathsf{R}_X(\ell, v), \mathsf{RMW}_X(\ell, v, v_{\text{new}})\}$ etc.  $\mathsf{rsElem}(a, b) \stackrel{\text{def}}{=} \mathsf{sameThread}(a, b) \lor \mathsf{isrmw}(b)$  $\mathsf{rseq}(a) \stackrel{\text{def}}{=} \{a\} \cup \{b \mid \mathsf{rsElem}(a, b) \land \mathsf{mo}(a, b) \land (\forall c. \ \mathsf{mo}(a, c) \land \mathsf{mo}(c, b) \Rightarrow \mathsf{rsElem}(a, c))\}$  $sw \stackrel{\text{def}}{=} \{(a, b) \mid \mathsf{mode}(a) \in \{\mathrm{rel}, \mathrm{rel}_{acq}, \mathrm{sc}\} \land \mathsf{mode}(b) \in \{\mathrm{acq}, \mathrm{rel}_{acq}, \mathrm{sc}\} \land \mathsf{rf}(b) \in \mathsf{rseq}(a)\}$  $\mathsf{hb} \stackrel{\mathrm{def}}{=} (\mathsf{sb} \cup \mathsf{sw})^+$  $\mathsf{hb}_{\ell} \stackrel{\text{def}}{=} \{(a, b) \in \mathsf{hb} \mid \mathsf{iswrite}_{\ell}(a) \land \mathsf{iswrite}_{\ell}(b)\}$  $X_{\mathsf{SegCst}} \stackrel{\text{def}}{=} \{(a, b) \in X \mid \mathsf{isSeqCst}(a) \land \mathsf{isSeqCst}(b)\}$  $\operatorname{isc}(a,b) \stackrel{\text{def}}{=} \operatorname{iswrite}_{\operatorname{locs}(b)}(a) \wedge \operatorname{sc}(a,b) \wedge \nexists c. \operatorname{sc}(a,c) \wedge \operatorname{sc}(c,b) \wedge \operatorname{iswrite}_{\operatorname{locs}(b)}(c)$

**Figure 3.** Axioms satisfied by consistent C11 executions, Consistent(A, lab, sb, rf, mo, sc).

| $c: W(\ell, 1) \xrightarrow{rf} a: R(\ell, 1)$ $\uparrow^{mo} \qquad hb \downarrow$ $d: W(\ell, 2) \xrightarrow{rf} b: R(\ell, 2)$ | $\begin{array}{c} c: \mathrm{W}(\ell,2) \xrightarrow[]{\text{mo}} a: \mathrm{W}(\ell,1) \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & $ | $\begin{array}{c} c: \mathrm{W}(\ell,1) \xrightarrow[]{rf} a: \mathrm{R}(\ell,1) \\ & \overbrace{mo}^{rf} b \downarrow \\ & b: \mathrm{W}(\ell,2) \end{array}$ | $a \xrightarrow{mo} b$        | means | a = rf(b) $mo(a, b)$ |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------|----------------------|

| violates CoherentRR                                                                                                                | violates CoherentWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | violates CoherentRW                                                                                                                                            | $a \xrightarrow{\text{nb}} b$ | means | hb(a,b)              |

Figure 4. Sample executions violating coherency conditions (Batty et al. 2011).

**Consistent Executions** According to the C11 model, an execution is consistent, Consistent(A, lab, sb, rf, mo, sc), if all of the properties shown in Figure 3 hold.

- (IrreflexiveHB) The happens-before order, hb, must be irreflexive: an action cannot happen before itself.

- (ConsistentMO) All write actions on an atomic location  $\ell$ must be totally ordered by mo, and be consistently ordered by hb (restricted to the location  $\ell$ ).

- (ConsistentSC) The sc relation must be a total order and include both hb and mo restricted to SC actions. This in effect means that SC actions are globally synchronized.

- (ConsistentRFdom) The reads-from map, rf, is defined for those read (or RMW) actions for which the execution contains an earlier write (or RMW) to the same location.

- (ConsistentRF) Each entry in the reads-from map, rf, should map a read to an earlier or concurrent write to the same location and with the same value.

- (ConsistentRFna) Further, if a read reads from a write and either the read or write are non-atomic, then the write must have happened before the read. Batty et al. (2011) also require the write to be *visible*: i.e. not to have been overwritten by another write that happened before the read. This extra condition is unnecessary, as it follows from CoherentWR.

- (RestrSCReads) SC reads are further restricted to read only from the immediately preceding SC write to the same location in sc order or from a non-SC write that has not happened before that immediately preceding SC write.

- (CoherentRR,CoherentWR,CoherentRW) Next, we have three per-location coherence properties relating mo, hb, and rf. These properties require that mo never contradicts hb or the observed read order, and that rf never reads values that have been overwritten by more recent actions that happened before the read. These coherence properties are depicted in Figure 4.

- (AtomicRMW) Each read-modify-write action should execute atomically: it should read from the immediately preceding write in mo.

- (ConsistentAlloc) Finally, the same location cannot be allocated twice by different allocation actions.<sup>2</sup>

**Remark** Our model differs in a few minor ways from that of Batty et al. (2011, 2012). First, we have incorporated the C standard's "additional synchronized with" (asw) relation in sb rather than in sw, because it describes synchronization induced by control flow rather than by data flow.

Second, our sw-relation also relates acquire reads with release writes (whenever the read returns a value written by or after the release write), even if the two actions belong

$$\begin{array}{l} \textbf{let } a = \textbf{alloc}() \textbf{ in} \\ \textbf{let } c = \textbf{alloc}() \textbf{ in} \\ [c]_{rlx} := 0; \\ \left( \begin{array}{c} [a]_{na} := 7; \\ [c]_{rel} := 1 \end{array} \right\| \begin{array}{c} \textbf{repeat} \ [c]_{acq} \ \textbf{end}; \\ [a]_{na} := [a]_{na} + 1 \end{array} \right) \end{array}$$

**Figure 5.** Message passing example showing transfer of ownership of the non-atomic location *a*.

to the same thread (and are thus sb-related), whereas Batty et al. (2012) do not add any sb-related actions to the swrelation. Since relating such actions also by sw does not affect execution consistency, we do so for uniformity, which eases the definition of validity of Hoare triples in §7.

Finally, in the standard, the sb and sw relations are taken to be strict partial orders, corresponding to the transitive closure of our relations. Conversely, our sb relation can be defined in terms of the sb order from the C and C++ standards as follows,  $sb_{our} = \{(a, b) \in sb_{std} \cup asw_{std} \mid \\ \nexists c. (a, c) \in sb_{std} \cup asw_{std} \land (c, b) \in sb_{std} \cup asw_{std}\}$ . Again, we found the non-transitive versions slightly more convenient when defining the meaning of Hoare triples.

#### 4. Relaxed Separation Logic

To motivate RSL, consider the message passing program shown in Figure 5. The thread on the left updates some data structure using non-atomic memory accesses (here, the location a), and then signals to other threads that the data structure has been updated by performing a release write to c. The thread on the right repeatedly performs acquire reads until it notices that  $[c] \neq 0$ . Then, it can conclude that the thread on the left has finished its work, and so may safely access the data structure without interfering with it.

This message passing idiom is correct (i.e., race-free) because whenever an acquire read sees the value written by a release write, the write "synchronizes with" the acquire read. Thus, as hb is transitive, any event that happened before the write (e.g., by being sequenced before it), also happens before the read. This, in turn, justifies the ownership transfer from the writing thread to the reading thread.

To model such ownership transfers, RSL extends the grammar of separation logic assertions, P, with three new assertion forms, Rel(e, Q), Acq(e, Q), and RMWAcq(e, Q), where Q ranges over functions from values to assertions. Formally, RSL assertions are given by following grammar:

$$\begin{array}{l} P,Q ::= \mathsf{false} \mid P \Rightarrow Q \mid \forall x. \ P \mid \mathsf{emp} \mid e \stackrel{k}{\mapsto} e' \mid P \ast Q \\ \mid \mathsf{Rel}(e,\mathcal{Q}) \mid \mathsf{Acq}(e,\mathcal{Q}) \mid \mathsf{RMWAcq}(e,\mathcal{Q}) \\ \mid \mathsf{Init}(e) \mid \mathsf{Uninit}(e) \end{array}$$

where k ranges over fractional permissions (Perm = (0, 1], see Boyland 2003). We have the usual classical first order logic constructs (the three primitive ones and the derived: true,  $\land$ ,  $\lor$ ,  $\neg$ ,  $\exists$ ), the three assertions forms pertinent to separation logic (empty heap, a single memory cell with

$<sup>^2</sup>$  This axiom suffices, because we do not support deallocation. Had we included deallocation, we would instead require there to be a deallocation actions between any two allocation actions of the same location. The formalized C11 model by Batty et al. (2011, 2012) does not model allocation.

| $\overline{\{P\} e \{y. P \land y = e\}}$ $\{P\} E_1 \{x. Q\}  \forall x. \{Q\} E_2 \{y. R\}$                                                                                                                    | $\frac{\{P\} E \{y, Q\}}{\{P * R\} E \{y, Q * R\}}$                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| $\{P\} \mathbf{let} \ x = E_1 \mathbf{in} \ E_2 \left\{y. \ R\right\}$                                                                                                                                           | $ \{P\} E \{y, Q\}  P' \Rightarrow P  \forall y, Q \Rightarrow Q' $                                       |

| $\frac{\{P \land b\} E_1 \{y. Q\}}{\{P \land \neg b\} E_2 \{y. Q\}}$ $\frac{\{P\} \text{ if } b \text{ then } E_1 \text{ else } E_2 \{y. Q\}}{\{P\} \text{ if } b \text{ then } E_1 \text{ else } E_2 \{y. Q\}}$ | $\{P'\} E \{y, Q'\}$                                                                                      |

| $\{P\} E \{y, Q\}  Q[0/y] \Rightarrow P$                                                                                                                                                                         | $\frac{\{P\} E \{y. Q\}}{\{P'\} E \{y. Q'\}} \frac{\{P'\} E \{y. Q'\}}{\{P \lor P'\} E \{y. Q \lor Q'\}}$ |

| $ \{P\} \text{ repeat } E \text{ end } \{y. \ Q \land y \neq 0\} $ $ \frac{\{P_1\} E_1 \{y. \ Q_1\}  \{P_2\} E_2 \{Q_2\}}{\{P_1 * P_2\} E_1 \ E_2 \{y. \ Q_1 * Q_2\}} $                                          | $\frac{\{P\} E \{y, Q\}}{\{\exists x. P\} E \{y, \exists x. Q\}}$                                         |

Figure 6. Standard proof rules supported by RSL.

fractional permission k, and separating conjunction), and five new forms, which we will explain shortly.

RSL judgements are of the form  $\{P\} E \{y, Q\}$ , where Pand Q are assertions respectively denoting the precondition and the postcondition of the expression E. The postcondition, Q, also describes the return value of the expression E, which is bound by the variable y. In cases where the postcondition does not describe the return value, we often omit the y binder. With this setup, we support all the standard rules from Hoare and separation logic (see Figure 6) including the so-called 'structural' rules: the frame, consequence, disjunction, and existential rules.

Another generic rule we support is the RELAX rule below. Generally, when reasoning about a program E, we are always allowed to reason about a relaxation of the program  $E' \sqsubseteq E$ , which is identical to E except on the atomic access annotations, which may be weaker than those of E according to the partial order: rlx  $\sqsubseteq$  rel  $\sqsubseteq$  sc, rlx  $\sqsubseteq$  acq  $\sqsubseteq$  sc.

$$\frac{\{P\} E' \{y, Q\} E' \sqsubseteq E}{\{P\} E \{y, Q\}}$$

(RELAX)

Atomic Writes We return to the treatment of atomic memory accesses and the new assertion forms. The first one,  $\text{Rel}(\ell, Q)$ , represents a permission to write any value v to location  $\ell$ , provided the assertion Q(v) holds separately. Performing the write consumes the Q(v) assertion so that it can be transferred to the reader(s).

$$\begin{cases} \mathcal{Q}(v) * \\ \mathsf{Rel}(\ell, \mathcal{Q}) \end{cases} [\ell]_{\mathrm{rel}} := v \begin{cases} \mathsf{Init}(\ell) * \\ \mathsf{Rel}(\ell, \mathcal{Q}) \end{cases}$$

(W-REL)

In order for the ownership transfer to be valid, the writer must synchronize with the reader(s), which means that the write must be at least of release kind (or stronger, namely SC). Besides the ownership transfer, the write also initializes the location  $\ell$ . Keeping track of initialized locations is necessary for subsequent proof rules. In the special case when no ownership transfer occurs (i.e., when P = emp), intuitively we can also use a relaxed write as in the following rule.

$$\left\{\mathsf{Rel}(\ell, v, \mathsf{emp})\right\} [\ell]_{\mathrm{rlx}} := v \left\{\mathsf{Init}(\ell)\right\} \qquad (W-\mathsf{RLX}^*)$$

In this rule, we used the following shorthand notation

$$\operatorname{\mathsf{Rel}}(\ell, v, P) \stackrel{\text{def}}{=} \operatorname{\mathsf{Rel}}(\ell, \lambda x. \text{ if } x = v \text{ then } P \text{ else false})$$

for representing the permission to write only the value v and release ownership of P (in this case emp). Intuitive though this rule is, it is unfortunately unsound in C11, as we will explain in Section 6, where we also show that we can restore its soundness by mildly strengthening the model.

In RSL, we allow multiple concurrent writes to the same atomic location by making the permission to perform an atomic write splittable as follows:

$$\begin{array}{l} \mathsf{Rel}(\ell, \mathcal{Q}_1) * \mathsf{Rel}(\ell, \mathcal{Q}_2) \\ \iff \mathsf{Rel}(\ell, \lambda v. \ \mathcal{Q}_1(v) \lor \mathcal{Q}_2(v)) \end{array} (\mathsf{REL-SPLIT})$$

Of course, programs that perform multiple concurrent writes to same location and transfer away ownership may leak memory, as some of the writes may be overwritten and thus never read. In this paper, however, we do not regard such memory leaks as an error. If desired, the programmer may explicitly count the number of allocations and deallocations in order to prove that the program has no memory leaks.

Similar to write permissions, the fact that a location has been initialized—captured by  $lnit(\ell)$ —can be freely duplicated. Once a location is initialized, it remains initialized: it cannot be de-initialized.

$$\operatorname{Init}(\ell) \iff \operatorname{Init}(\ell) * \operatorname{Init}(\ell)$$

(INIT-SPLIT)

Atomic Reads The second assertion form,  $Acq(\ell, Q)$ , denotes a permission to perform an acquire read of location  $\ell$  and obtain ownership of Q(v), where v is the value read.

$$\frac{\forall x. \operatorname{precise}(\mathcal{Q}(x))}{\left\{ \begin{array}{c} \operatorname{Init}(\ell) * \\ \operatorname{Acq}(\ell, \mathcal{Q}) \end{array} \right\} [\ell]_{\operatorname{acq}} \left\{ \begin{array}{c} v. \ \mathcal{Q}(v) * \\ \operatorname{Acq}(\ell, \mathcal{Q}[v:=\mathsf{emp}]) \end{array} \right\}} \quad (\text{R-ACQ})$$

The premise of the rule (that Q should be precise) is a technical requirement that will be explained in Section 7 and may be ignored for the time being. As a precondition, we require not only the permission to perform an acquire read from  $\ell$ , but also the knowledge that the location has been initialized. The latter is needed because reading from uninitialized locations may return any arbitrary value and thus we cannot ensure that Q(v) was ever established. When reading a value, we acquire Q(v) and give up the permission to read the same value again with ownership transfer, because otherwise it would have been possible to acquire the same Q(v) multiple times. Therefore, in the postcondition the assertion attached to the acquire predicate becomes

$$\mathcal{Q}[v:=\mathsf{emp}] \stackrel{\mathrm{def}}{=} \lambda y.$$

if  $y=v$  then emp else  $\mathcal{Q}(y)$ .

This allows further reads of the same value, but consequent reads will simply not gain any ownership. At any point, it is also possible to do a relaxed read and acquire no ownership.

$$\left\{\mathsf{Init}(\ell) * \mathsf{Acq}(\ell, \mathcal{Q})\right\} [\ell]_{\mathrm{rlx}} \left\{\mathsf{Acq}(\ell, \mathcal{Q})\right\} \qquad (\mathsf{R}\text{-}\mathsf{RLX})$$

Note that this rule does not assert anything about the value read. A more useful rule is the following, which asserts that the value read must be one that may have been written.

$$\begin{cases} \mathsf{Init}(\ell) * \\ \mathsf{Acq}(\ell, \mathcal{Q}) \end{cases} [\ell]_{\mathrm{rlx}} \begin{cases} v. \ \mathsf{Acq}(\ell, \mathcal{Q}) \land \\ (\mathcal{Q}(v) \neq \mathsf{false}) \end{cases}$$

(R-RLX\*)

Similar to W-RLX\*, this latter rule is not sound in C11, but is so in the strengthened model of Section 6.

In RSL, we permit multiple readers to read the value written by a single release write. Concretely, consider the scenario where thread A initializes two data structures and signals by a release write that it has finished its work. Then thread B can do an acquire read and notice that A has finished its initialization and then access the first data structure non-atomically. Likewise, thread C can do an acquire read and access the second data structure non-atomically. Such an execution does not have data races and should therefore be permitted. In terms of our program logic, this means that acquire read permissions should be splittable and joinable as follows:

$$\begin{array}{l} \mathsf{Acq}(\ell, \mathcal{Q}_1) * \mathsf{Acq}(\ell, \mathcal{Q}_2) \\ \iff \mathsf{Acq}(\ell, \lambda v. \, \mathcal{Q}_1(v) * \mathcal{Q}_2(v)) \end{array} \tag{ACQ-SPLIT}$$

**Read-Modify-Write Instructions** The next new assertion form, RMWAcq $(\ell, Q)$ , is used in the following proof rule for atomic compare-and-swaps.

$$P \Rightarrow \operatorname{Init}(\ell) * \operatorname{RMWAcq}(\ell, \mathcal{Q}) * \operatorname{true} P * \mathcal{Q}(v) \Rightarrow \operatorname{Rel}(\ell, \mathcal{Q}') * \mathcal{Q}'(v') * R[v/y]$$

$$X \in \{\operatorname{rel}, \operatorname{rlx}\} \Rightarrow \mathcal{Q}(v) = \operatorname{emp} X \in \{\operatorname{acq}, \operatorname{rlx}\} \Rightarrow \mathcal{Q}'(v') = \operatorname{emp} \frac{\{P\} \left[\ell\right]_Y \{y. \ y \neq v \Rightarrow R\}}{\{P\} \operatorname{CAS}_{X,Y}(\ell, v, v') \{y. R\}} \quad (\operatorname{CAS}^*)$$

The rule has five premises. First, the precondition must ensure that we have permission to do a RMW-read from  $\ell$ and acquire ownership of Q(v). Second, we require the update performed by the successful **CAS** to be valid: that is, to have the necessary release permission, to satisfy Q'(v'), the assertion that is to be transferred away, and to separately also satisfy the postcondition. As a precondition for this update, we get to assume not only that the initial precondition holds, but also that we have access to the state acquired by ownership transfer, Q(v).

The next two premises take the access modes into account, suitably restricting the ownership that can be acquired or released. If the successful **CAS** is of release or relaxed kind, then it does not synchronize with the write whose value it read, so it should not acquire any ownership. This is ensured by demanding that Q(v) = emp. Symmetrically, if the successful **CAS** is of acquire or relaxed kind, it does not synchronize with the reads seeing the value it produced, so it should not release any ownership. This is ensured by demanding that Q'(v') = emp.

Finally, we require that failed **CASs** also satisfy the postcondition, R, under the assumption that a value different from the expected one was read.

In its general form, the CAS\* rule is sound in the strengthened model of Section 6. In the standard model, it is sound only when  $X \in {\text{rel}\_acq, sc}$ .

Unlike multiple normal reads, multiple successful **CAS** instructions cannot all read from (and therefore potentially synchronize with) the same write. This follows from the AtomicRMW axiom, which requires RMW actions to read from the immediately preceding write in mo-order. Therefore, it is sound to duplicate the RMW-acquire permission,

$$\begin{array}{l} \mathsf{RMWAcq}(\ell,\mathcal{Q}) \\ \Longleftrightarrow \ \mathsf{RMWAcq}(\ell,\mathcal{Q}) * \mathsf{RMWAcq}(\ell,\mathcal{Q}) \end{array} (\mathsf{RMW-SPLIT}) \end{array}$$

because the semantics ensures that at most one process will effectively be able to use this permission at any given instant.

In order to be able to prove the last premise of the CAS\* rule, we also support the following rule, allowing us to carve out a plain acquire permission from an RMW-acquire one.

$$\frac{\forall v. \ \mathcal{Q}'(v) = \mathsf{emp} \lor \mathcal{Q}(v) = \mathcal{Q}'(v) = \mathsf{false}}{\mathsf{RMWAcq}(\ell, \mathcal{Q}) \iff \mathsf{RMWAcq}(\ell, \mathcal{Q}) * \mathsf{Acq}(\ell, \mathcal{Q}')}$$

(RMW-ACQ-SPLIT)

The premise of RMW-ACQ-SPLIT ensures that the assertion that we have carved out for plain reads is empty, except perhaps for the values where Q(v) is false, in which case Q'(v) may also be false.

Allocation of Atomic Locations Whenever a new atomic location is allocated, the verifier is free to choose a suitable ownership assertion Q and attach it to the newly allocated location, and moreover to choose whether the ownership of Q will be acquired using plain reads or using successful CASs. We thus have the following two rules.

$$\{ \mathsf{emp} \} \mathbf{alloc}() \{ \ell. \operatorname{Rel}(\ell, \mathcal{Q}) * \operatorname{Acq}(\ell, \mathcal{Q}) \}$$

(A-R)

$$\{ \mathsf{emp} \} \mathbf{alloc}() \{ \ell. \operatorname{Rel}(\ell, \mathcal{Q}) * \operatorname{RMWAcq}(\ell, \mathcal{Q}) \}$$

(A-M)

Following the C standard, newly allocated locations are not initialized, and thus do not generate the  $Init(\ell)$  permission required for reading them. To enable reading from these locations, the programmer must first initialize them by performing a plain write as we have already seen.

*Non-Atomic Locations* Finally, the rules for non-atomic accesses are exactly as in concurrent separation logic. Allocation returns an uninitialized new cell with full permission; writing requires full permission of a location (whether initialized or not), whereas reading works also with partial permission but requires the location to be initialized.

$$\{emp\} alloc() \{x. Uninit(x)\}$$

(A-NA)

$$\left\{\ell \stackrel{1}{\mapsto} - \vee \mathsf{Uninit}(\ell)\right\} [\ell]_{\mathrm{na}} := v \left\{\ell \stackrel{1}{\mapsto} v\right\}$$

(W-NA)

$$\left\{\ell \stackrel{k}{\mapsto} v\right\} [\ell]_{\mathrm{na}} \left\{x. \ x = v \land \ell \stackrel{k}{\mapsto} v\right\} \quad (\mathrm{R}\text{-}\mathrm{NA})$$

| Let $Q_J(v) \stackrel{\text{def}}{=} (v = 0 \land \text{emp}) \lor (v = 1 \land J)$ |                                                                                             |  |  |  |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

|                                                                                     | $) * RMWAcq(x, \mathcal{Q}_J) * Init(x)$                                                    |  |  |  |

| $new\_lock() \stackrel{\text{def}}{=}$                                              | $lock(x) \stackrel{\text{def}}{=}$                                                          |  |  |  |

| $\{J\}$                                                                             | $\{Lock(x,J)\}$                                                                             |  |  |  |

| $\mathbf{let} \ x = \mathbf{alloc}(\mathbf{)} \ \mathbf{in}$                        | repeat                                                                                      |  |  |  |

| $\int J * \operatorname{Rel}(x, \mathcal{Q}_J) * $                                  | $\{Lock(x,J)\}$                                                                             |  |  |  |

| $\left\{RMWAcq(x,\mathcal{Q}_J)\right\}$                                            | spin(x);                                                                                    |  |  |  |

| $[x]_{\mathrm{rel}} := 1$                                                           | $\{Lock(x,J)\}$                                                                             |  |  |  |

| $\left\{Lock(x,J)\right\}$                                                          | $\mathbf{CAS}_{\mathrm{acq,rlx}}(x,1,0)$                                                    |  |  |  |

| $unlock(x) \stackrel{\text{def}}{=}$                                                | $ \begin{cases} y. \ Lock(x, J) * \\ (y = 1 \land J \lor \\ y = 0 \land emp ) \end{cases} $ |  |  |  |

| $\{J * Lock(x, J)\}$                                                                | $\left\{ \begin{array}{c} \left( y = 1 \land J \lor \right) \right\}$                       |  |  |  |

| $[x]_{\mathrm{rel}} := 1$                                                           | $ ( y = 0 \land emp ) $                                                                     |  |  |  |

| $\{\operatorname{lnit}(x) * Lock(x, J)\}$                                           | end                                                                                         |  |  |  |

| $\left\{Lock(x,J)\right\}$                                                          | $\left\{J * Lock(x, J)\right\}$                                                             |  |  |  |

Figure 7. Verification of the lock module.

def