# Relaxed Separation Logic: A Program Logic for C11 Concurrency

Viktor Vafeiadis

Max Planck Institute for Software Systems

(MPI-SWS)

viktor@mpi-sws.org

Chinmay Narayan

Indian Institute of Technology, Delhi chinmay@cse.iitd.ac.in

## **Abstract**

We introduce *relaxed separation logic* (RSL), the first program logic for reasoning about concurrent programs running under the C11 relaxed memory model. From a user's perspective, RSL is an extension of concurrent separation logic (CSL) with proof rules for the various kinds of C11 atomic accesses. As in CSL, individual threads are allowed to access non-atomically only the memory that they own, thus preventing data races. Ownership can, however, be transferred via certain atomic accesses. For SC-atomic accesses, we permit arbitrary ownership transfer; for acquire/release atomic accesses, we allow ownership transfer only in one direction; whereas for relaxed atomic accesses, we rule out ownership transfer completely. We illustrate RSL with a few simple examples and prove its soundness directly over the axiomatic C11 weak memory model.

Categories and Subject Descriptors D.3.1 [Programming Languages]: Formal Definitions and Theory; F.3.1 [Logics and Meanings of Programs]: Specifying and Verifying and Reasoning about Programs

**Keywords** Concurrency; Weak memory models; C/C++; Proof system; Separation logic

## 1. Introduction

Wanting to enable many hardware and software optimizations, modern programming language definitions provide rather weak guarantees on the semantics of concurrent memory accesses allowing, for example, different threads to observe shared operations happening in different orders. One such case is the concurrency model adopted by the 2011 revisions of the C and C++ standards (ISO/IEC 9899:2011;

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

OOPSLA '13, October 29–31, 2013, Indianapolis, Indiana, USA. Copyright is held by the owner/author(s). Publication rights licensed to ACM. ACM 978-1-4503-2374-1/13/10...\$15.00. http://dx.doi.org/10.1145/2509136.2509532

ISO/IEC 14882:2011), which we will study in this paper and refer to as the C11 model.

C11 provides several kinds of memory accesses—non-atomic, relaxed atomic, acquire atomic, release atomic, and sequentially consistent (SC) atomic—each providing different consistency guarantees. On the one end of the spectrum, races on non-atomic accesses result in completely undefined behaviour (they are treated as programming errors); on the other end, SC-atomic accesses are globally synchronized. The guarantees provided by relaxed, acquire, and release accesses lie somewhere in between: different threads can observe them happening in different orders.

The reason for having all these kinds of accesses is that they map differently to the various common architectures, and have very different implementation costs. Non-atomic and relaxed atomic accesses are generally rather cheap as they correspond to vanilla machine loads and stores, and may be reordered by the compiler and/or by an out-of-order execution unit. At the other end of the spectrum, SC accesses are very expensive because their implementation involves a full memory barrier. The cost of acquire and release accesses depends a lot on the architecture. On x86, they are compiled down to plain reads and writes (Batty et al. 2011) and are therefore cheap. On PowerPC and ARM, the cost is somewhat higher as they induce a memory barrier, but of a weaker kind than full memory barriers (Sarkar et al. 2012).

Our goal is to help C11 programmers by providing them with sound reasoning principles for concurrent programs. We show that C11 concurrency supports resource reasoning in the style of separation logic (O'Hearn 2007); in particular, ownership can be transferred along acquire/release atomic memory accesses and does not require SC-accesses.

We develop relaxed separation logic (RSL), a program logic that follows the resourceful reading of separation logic triples. When we assert the Hoare triple  $\{P\}$  Cmd  $\{Q\}$ , we say that the command Cmd will not access any memory other than that given by its precondition, P, or subsequently acquired during its execution. We thus support the parallel composition rule of separation logic,

$$\frac{\left\{P_{1}\right\} C m d_{1}\left\{Q_{1}\right\}}{\left\{P_{1}*P_{2}\right\} C m d_{1} \left\|C m d_{2}\left\{Q_{1}*Q_{2}\right\}} \qquad (\text{PAR})$$

which ensures that the two threads do not have any races on non-atomic memory accesses, a condition required by C11.

To handle acquire/release atomics, we introduce two new assertion kinds,  $\operatorname{Rel}(\ell, \mathcal{Q}_1)$  and  $\operatorname{Acq}(\ell, \mathcal{Q}_2)$ . These denote respectively the permissions to perform a release-write of some value v at location  $\ell$  and give away ownership of the resource described by  $\mathcal{Q}_1(v)$ , or an acquire-read and gain ownership of  $\mathcal{Q}_2(v)$ . With these assertion forms we provide simple proof rules for release writes and acquire reads, similar to those for releasing and acquiring mutual exclusion locks in concurrent separation logic.

Besides RSL itself, the main contribution of this work was to define the meaning of Hoare triples in a relaxed memory model setting, so as to prove the soundness of RSL. This was rather challenging for three main reasons.

No global state/time: Traditionally,  $\{P\}$  Cmd  $\{Q\}$  asserts that if we execute Cmd in an initial state satisfying P and it terminates, then the final state will satisfy Q. In C11 concurrency, however, the terms "initial state" and "final state" are ill-defined, because there exist no global notions of time or state.

To interpret triples, we thus resort to *logical* local notions of time and state. We define a logical notion of local state at each event of a program execution, and thread the logical state through C11 "happens-before" edges.

**Assertions in heaps:** Our assertions for dealing with acquire and release atomics require that the logical heaps used to interpret them contain assertions. This results in a circularity in the model of assertions, which for simplicity we resolve by storing syntactic assertions.

No operational semantics: Concurrent program logics are typically proved sound over an operational or a trace semantics. In either case, the meaning of Hoare triples can be defined in terms of an auxiliary predicate by induction over the length of an execution trace. These definitions cannot directly be extended to the C11 model as there is no obvious total order for the induction. Our solution is to order the C11 events according to the total number of events that happen before them.

As a secondary contribution, we observed that the semantics of relaxed atomic memory accesses in C11 is too weak to permit even the most basic reasoning principles about them, which in turn renders basic compiler optimizations unsound. In order to allow such reasoning principles, we proposed a crude fix to C11, which we discuss in Section 6.

In the remainder of this paper, we define a minimal concurrent programming language (§2), review the C11 concurrency model (§3), describe the assertions and proofs rules of RSL (§4), verify a few examples using RSL (§5), explain the problems caused by relaxed accesses and their resolution (§6), present the semantics of assertions and Hoare triples and sketch the main parts of the soundness proof (§7). We conclude with a discussion of related and future work (§8).

A Coq formalization of the soundness proof of RSL can be found at the following URL.

http://www.mpi-sws.org/~viktor/rsl/

# 2. Programming Language

In order to focus on the concurrency aspects of C11 and to avoid the inherent complexity of a large language like C, we introduce a minimal concurrent programming language featuring the various kinds of memory accesses supported by C11. Following Batty et al. (2012), we omit consume reads from the model, because they are relevant only for a few architectures (PowerPC and ARM) and substantially complicate the model. For simplicity, we also omit memory fences.

To make the local sequential execution order explicit, we present the grammar of expressions in A-normal form (cf. Flanagan et al. 1993). Atomic expressions,  $e \in AExp$ , consist of variables and values (locations and numbers). Program expressions,  $E \in Exp$ , consist of atomic expressions, let-bound computations, conditionals, loops, parallel composition, memory allocation, loads, stores, and atomic compare-and-swap (CAS) instructions.

```

\begin{array}{ll} v \in \mathsf{Val} ::= \ell \mid n & \text{where } \ell \in \mathsf{Loc}, n \in \mathbb{N} \\ e \in \mathsf{AExp} ::= x \mid v & \text{where } x \in \mathsf{Var} \\ E \in \mathsf{Exp} ::= e \mid \mathbf{let} \ x = E \ \mathbf{in} \ E' \mid \mathbf{if} \ e \ \mathbf{then} \ E \ \mathbf{else} \ E' \\ \mid \mathbf{repeat} \ E \ \mathbf{end} \mid E_1 \parallel E_2 \mid \mathbf{alloc}() \\ \mid [e]_X \mid [e]_Y := e' \mid \mathbf{CAS}_{Z,W}(e,e',e'') \\ \mathbf{where} \ X \in \{ \mathbf{sc}, \mathbf{acq}, \mathbf{rlx}, \mathbf{na} \}, Y \in \{ \mathbf{sc}, \mathbf{rel}, \mathbf{rlx}, \mathbf{na} \}, \\ Z \in \{ \mathbf{sc}, \mathbf{rel} \_ \mathbf{acq}, \mathbf{acq}, \mathbf{rel}, \mathbf{rlx} \}, W \in \{ \mathbf{sc}, \mathbf{acq}, \mathbf{rlx} \} \end{array}

```

As in C, in conditional expressions we treat zero as false and non-zero values as true. The construct  $\mathbf{repeat}\ E$  end executes E repeatedly until it returns a non-zero value.

Memory accesses are annotated by their mode: sequentially consistent (sc), acquire (acq), release (rel), combined release-acquire (rel\_acq), relaxed (rlx), or non-atomic (na). According to the C standard, not all modes are available for all accesses: reads cannot be releases, writes cannot be acquires, CASs cannot be non-atomic. These restrictions are to avoid redundancy in the language. For example, an acquire write, if such a thing were allowed, would behave exactly the same as a relaxed write.

CAS is an atomic operation used to heavily in lock-free concurrent algorithms. It takes a location,  $\ell$ , and two values, v' and v'', as arguments. It atomically checks if the value at location is v' or not. If the value is same as v', then CAS succeeds: it atomically writes v'' to  $\ell$  and returns the old value. If the value is different, CAS fails: it returns that value and does not modify the location. CAS is annotated with two access modes: one to be used for the successful case, and one for the unsuccessful case.

For conciseness in examples, we will often write expressions such as  $[E]_{na}$  instead of let x = E in  $[x]_{na}$ . We also write  $E_1$ ;  $E_2$  instead of let  $x = E_1$  in  $E_2$  when  $x \notin fv(E_2)$ .

```

\begin{split} new\_lock() &= \mathbf{let} \ x = \mathbf{alloc}() \ \mathbf{in} \ [x]_{\mathrm{rel}} := 1; x \\ spin(x) &= \mathbf{repeat} \ [x]_{\mathrm{rlx}} \ \mathbf{end} \\ lock(x) &= \mathbf{repeat} \ spin(x); \mathbf{CAS}_{\mathrm{acq,rlx}}(x,1,0) \ \mathbf{end} \\ unlock(x) &= [x]_{\mathrm{rel}} := 1 \end{split}

```

Figure 1. Simple spinlock implementation.

Spinlock Example There are two important uses of acquire/release accesses: in implementing locks, and in message passing. Relaxed accesses are useful in cases of optimistic reads, where the value read, if it is of interest to the algorithm, will be read again by an acquire read, or an acquire fence will be issued. For example, in the simple CAS-based spinlock implementation shown in Figure 1, lock(x) performs an acquire-on-success CAS and unlock(x) does a release write. The optimistic spin(x) loop that waits for the lock to become free, in contrast, does relaxed reads. The combined release-acquire CAS is supposed to be used for operations that atomically release one lock and acquire another—this is possible, for example, if the locks are represented as different bits of the same word. Further examples can be found in McKenney and Garst (2011).

# 3. The C11 Memory Model

The C11 memory model is defined axiomatically in terms of program executions. A program *execution* consists of a set of actions and several binary relations over them. Actions describe the memory operations performed by the program, and are labelled with information about the memory order of the operation, the address accessed and the values read and/or written.

$$\begin{aligned} \mathsf{Act} &::= \mathrm{skip} \mid \mathbf{W}_{(\mathrm{sc|rel|rlx|na})}(\ell, v) \mid \mathbf{R}_{(\mathrm{sc|acq|rlx|na})}(\ell, v) \\ & \mid \mathbf{RMW}_{(\mathrm{sc|rel\_acq|acq|rel|rlx})}(\ell, v, v') \mid \mathbf{A}(\ell) \end{aligned}$$

In summary, we have a no-op action; SC, release, relaxed and non-atomic writes; SC, acquire, relaxed, and non-atomic reads; atomic read-modify-write actions; and allocations. The no-op (skip) action represents local computations, thread forks and joins.

For the subset of C11 we consider, an execution contains the following relations:<sup>1</sup>

- Sequenced-before (sb) relates actions of the same thread that follow one another in control flow. We have sb(a, b) if a and b belong to the same thread and a immediately precedes b in the thread's control flow, or a is a fork action and b the first action of the forked thread, or b is a join action and a the last action of the joined thread.

- The reads-from map (rf) maps every read action r to the write action w that wrote the value read by r.

- The *memory-order* relation (mo) is a total order on the store actions writing to the same atomic location.

- The sequential-consistency order (sc) is a total order over all SC-atomic actions.

Formally, let AName be a countably infinite of action names. Then, an execution,  $\mathcal{X}$ , is represented as a tuple,  $\langle \mathcal{A}, \mathsf{lab}, \mathsf{sb}, \mathsf{rf}, \mathsf{mo}, \mathsf{sc} \rangle$ , where  $\mathcal{A} \subseteq_{\mathrm{fin}} \mathsf{AName}$  is the set of action names included in the execution,  $\mathsf{lab} \in \mathcal{A} \to \mathsf{Act}$  maps every action identifier to its label,  $\mathsf{rf} \in \mathcal{A} \to \mathcal{A}$  is the reads-from map, and  $\mathsf{sb}, \mathsf{mo}, \mathsf{sc} \in \mathcal{P}(\mathcal{A} \times \mathcal{A})$  are the sequenced-before relation, the memory order, and the sequential consistency order respectively.

From these relations, C11 defines a number of derived relations, the most important of which are: the *synchronizes-with* relation and the *happens-before* order.

- Synchronizes-with (sw) relates acquire reads with the release writes that precede in mo order the write whose value was read by the acquire read provided that all the writes between these two writes belong to the same thread or are RMW operations.

- *Happens-before* (hb) is a partial order on actions formalizing the intuition that one action was completed before the other. In the C11 subset we consider, hb = (sb∪sw)<sup>+</sup>.

The semantics of a program is given by the set of *consistent* executions. An execution is said to be consistent if it satisfies the axioms of the memory model, which will be presented shortly. If, however, any of these consistent executions contains a data race on non-atomic actions, i.e. events generated from two conflicting operations on the same non-atomic location not ordered by hb in either direction, then the program is deemed to have arbitrary semantics. Thus, any sound program logic for C11 concurrency must ensure its specifications imply race-freedom for non-atomic actions.

**Expression Semantics** Let CExp denote closed expressions (i.e., ones with no free variables). The semantics of such closed expressions,  $[\![E]\!]$ , is given in Figure 2 as a set of tuples  $\langle res, \mathcal{A}, \mathsf{lab}, \mathsf{sb}, fst, lst \rangle$ . These tuples represent finite complete executions as well as finite incomplete execution prefixes (used to model infinite executions), where:

- (1) res is the result of evaluating the expression or  $\bot$  if the execution is incomplete;

- (2) A is the set of all actions contained in the execution;

- (3) lab labels the actions with the corresponding operations;

- (4) sb represents the sequenced-before relation; and

- (5) fst and lst are the first and last actions in the sb-order. For uniformity, we record the last action even in incomplete executions. In the parallel composition case, the auxiliary function combine( $res_1, res_2$ ) returns  $res_1$  if  $res_2 \neq \bot$  and  $\bot$  otherwise. In the  $\llbracket E \rrbracket$  semantics, allocations can return an arbitrary new location, and reads can read an arbitrary value. These will later be constrained by the consistency axioms.

$<sup>\</sup>overline{\ }^{1}$  The full model includes two additional relations, dd (data dependency) and dob (dependency ordered before), used to define the happens-before relation for consume reads.

```

\llbracket - \rrbracket \ : \ \mathsf{CExp} \to \mathbb{P}(\langle \mathit{res} : \mathsf{Val} \cup \{\bot\}, \mathcal{A} : \mathbb{P}(\mathsf{AName}), \mathsf{lab} : \mathcal{A} \to \mathsf{Act}, \mathsf{sb} : \mathbb{P}(\mathcal{A} \times \mathcal{A}), \mathit{fst} : \mathcal{A}, \mathit{lst} : \mathcal{A} \rangle)

\llbracket v \rrbracket \stackrel{\mathrm{def}}{=} \{ \langle v, \{a\}, \mathsf{lab}, \emptyset, a, a \rangle \mid a \in \mathsf{AName} \wedge \mathsf{lab}(a) = \mathsf{skip} \}

\llbracket \mathbf{alloc}() \rrbracket \stackrel{\mathrm{def}}{=} \{ \langle \ell, \{a\}, \mathsf{lab}, \emptyset, a, a \rangle \mid a \in \mathsf{AName} \land \ell \in \mathsf{Loc} \land \mathsf{lab}(a) = \mathsf{A}(\ell) \}

\llbracket [v]_Z := v' \rrbracket \stackrel{\mathrm{def}}{=} \{ \langle v', \{a\}, \mathsf{lab}, \emptyset, a, a \rangle \mid a \in \mathsf{AName} \wedge \mathsf{lab}(a) = \mathsf{W}_Z(v, v') \}

\llbracket [v]_Z \rrbracket \stackrel{\mathrm{def}}{=} \{ \langle v', \{a\}, \mathsf{lab}, \emptyset, a, a \rangle \mid a \in \mathsf{AName} \land v' \in \mathsf{Val} \land \mathsf{lab}(a) = \mathrm{R}_Z(v, v') \}

\llbracket \mathbf{let} \ x = E_1 \ \mathbf{in} \ E_2 \rrbracket \stackrel{\mathrm{def}}{=} \{ \langle \bot, \mathcal{A}_1, \mathsf{lab}_1, \mathsf{sb}_1, \mathit{fst}_1, \mathit{lst}_1 \rangle \mid \langle \bot, \mathcal{A}_1, \mathsf{lab}_1, \mathsf{sb}_1, \mathit{fst}_1, \mathit{lst}_1 \rangle \in \llbracket E_1 \rrbracket \}

\cup \{\langle res_2, \mathcal{A}_1 \uplus \mathcal{A}_2, \mathsf{lab}_1 \cup \mathsf{lab}_2, \mathsf{sb}_1 \cup \mathsf{sb}_2 \cup \{(\mathit{lst}_1, \mathit{fst}_2)\}, \mathit{fst}_1, \mathit{lst}_2 \rangle \mid

\langle v_1, \mathcal{A}_1, \mathsf{lab}_1, \mathsf{sb}_1, fst_1, lst_1 \rangle \in \llbracket E_1 \rrbracket \land \langle res_2, \mathcal{A}_2, \mathsf{lab}_2, \mathsf{sb}_2, fst_2, lst_2 \rangle \in \llbracket E_2[v_1/x] \rrbracket \rbrace

\llbracket E_1 \rVert E_2 \rrbracket \stackrel{\mathrm{def}}{=} \{ \langle \mathsf{combine}(\mathit{res}_1, \mathit{res}_2), \mathcal{A}_1 \uplus \mathcal{A}_2 \uplus \{ a_{\mathsf{fork}}, a_{\mathsf{join}} \}, \mathsf{lab}_1 \cup \mathsf{lab}_2 \cup \{ a_{\mathsf{fork}} \mapsto \mathsf{skip}, a_{\mathsf{join}} \mapsto \mathsf{skip} \},

\mathsf{sb}_1 \cup \mathsf{sb}_2 \cup \{(a_{\mathsf{fork}}, \mathit{fst}_1), (a_{\mathsf{fork}}, \mathit{fst}_2), (\mathit{lst}_1, a_{\mathsf{join}}), (\mathit{lst}_2, a_{\mathsf{join}})\}, a_{\mathsf{fork}}, a_{\mathsf{join}} \rangle \mid

\langle res_1, \mathcal{A}_1, \mathsf{sb}_1, fst_1, lst_1 \rangle \in \llbracket E_1 \rrbracket \land \langle res_2, \mathcal{A}_2, \mathsf{sb}_2, fst_2, lst_2 \rangle \in \llbracket E_2 \rrbracket \land a_{\mathrm{fork}}, a_{\mathrm{join}} \in \mathsf{AName} \}

Figure 2. Semantics of closed program expressions.

\nexists x. \mathsf{hb}(x,x)

(IrreflexiveHB)

\forall \ell. totalorder(\{a \in \mathcal{A} \mid \mathsf{iswrite}_{\ell}(a)\}, mo) \land \mathsf{hb}_{\ell} \subseteq \mathsf{mo}

(ConsistentMO)

\mathsf{totalorder}(\{a \in \mathcal{A} \mid \mathsf{isSeqCst}(a)\}, \mathsf{sc}) \land \mathsf{hb}_{\mathsf{SeqCst}} \subseteq \mathsf{sc} \land \mathsf{mo}_{\mathsf{SeqCst}} \subseteq \mathsf{sc}

(ConsistentSC)

\forall b. \ \mathsf{rf}(b) \neq \bot \iff \exists \ell, a. \ \mathsf{iswrite}_{\ell}(a) \land \mathsf{isread}_{\ell}(b) \land \mathsf{hb}(a,b)

(ConsistentRFdom)

\forall a, b. \ \mathsf{rf}(b) = a \implies \exists \ell, v. \ \mathsf{iswrite}_{\ell, v}(a) \land \mathsf{isread}_{\ell, v}(b) \land \neg \mathsf{hb}(b, a)

(ConsistentRF)

\forall a, b. \ \mathsf{rf}(b) = a \land (\mathsf{mode}(a) = \mathsf{na} \lor \mathsf{mode}(b) = \mathsf{na}) \implies \mathsf{hb}(a, b)

(ConsistentRFna)

\forall a, b. \ \mathsf{rf}(b) = a \land \mathsf{isSeqCst}(b) \implies \mathsf{isc}(a, b) \lor \neg \mathsf{isSeqCst}(a) \land (\forall x. \ \mathsf{isc}(x, b) \Rightarrow \neg \mathsf{hb}(a, x))

(RestrSCReads)

\nexists a, b. \ \mathsf{hb}(a, b) \land \mathsf{mo}(\mathsf{rf}(b), \mathsf{rf}(a)) \land \mathsf{locs}(a) = \mathsf{locs}(b)

(CoherentRR)

\nexists a, b. \ \mathsf{hb}(a, b) \land \mathsf{mo}(\mathsf{rf}(b), a) \land \mathsf{iswrite}(a) \land \mathsf{locs}(a) = \mathsf{locs}(b)

(CoherentWR)

\nexists a, b. \ \mathsf{hb}(a, b) \land \mathsf{mo}(b, \mathsf{rf}(a)) \land \mathsf{iswrite}(b) \land \mathsf{locs}(a) = \mathsf{locs}(b)

(CoherentRW)

\forall a. \; \mathsf{isrmw}(a) \land \mathsf{rf}(a) \neq \bot \implies \mathsf{mo}(\mathsf{rf}(a), a) \land \nexists c. \; \mathsf{mo}(\mathsf{rf}(a), c) \land \mathsf{mo}(c, a)

(AtomicRMW)

\forall a, b, \ell. \ \mathsf{lab}(a) = \mathsf{lab}(b) = \mathsf{A}(\ell) \implies a = b

(ConsistentAlloc)

where \mathsf{iswrite}_{\ell,v}(a) \stackrel{\mathsf{def}}{=} \exists X, v_{\mathsf{old}}. \, \mathsf{lab}(a) \in \{ \mathsf{W}_X(\ell,v), \mathsf{RMW}_X(\ell,v_{\mathsf{old}},v) \} \mathsf{iswrite}_{\ell}(a) \stackrel{\mathsf{def}}{=} \exists v. \, \mathsf{iswrite}_{\ell,v}(a)

\operatorname{isread}_{\ell,v}(a) \stackrel{\text{def}}{=} \exists X, v_{\text{new}}. \ \operatorname{lab}(a) \in \{ R_X(\ell, v), RMW_X(\ell, v, v_{\text{new}}) \}

rsElem(a, b) \stackrel{\text{def}}{=} sameThread(a, b) \lor isrmw(b)

\mathsf{rseq}(a) \stackrel{\mathrm{def}}{=} \{a\} \cup \{b \mid \mathsf{rsElem}(a,b) \land \mathsf{mo}(a,b) \land (\forall c.\ \mathsf{mo}(a,c) \land \mathsf{mo}(c,b) \Rightarrow \mathsf{rsElem}(a,c))\}

\mathsf{sw} \stackrel{\text{def}}{=} \{(a,b) \mid \mathsf{mode}(a) \in \{\mathsf{rel}, \mathsf{rel\_acq}, \mathsf{sc}\} \land \mathsf{mode}(b) \in \{\mathsf{acq}, \mathsf{rel\_acq}, \mathsf{sc}\} \land \mathsf{rf}(b) \in \mathsf{rseq}(a)\}

\mathsf{hb} \stackrel{\mathrm{def}}{=} (\mathsf{sb} \cup \mathsf{sw})^+

\begin{aligned} \mathsf{hb}_\ell &\stackrel{\mathrm{def}}{=} \{(a,b) \in \mathsf{hb} \mid \mathsf{iswrite}_\ell(a) \land \mathsf{iswrite}_\ell(b)\} \\ X_{\mathsf{SeqCst}} &\stackrel{\mathrm{def}}{=} \{(a,b) \in X \mid \mathsf{isSeqCst}(a) \land \mathsf{isSeqCst}(b)\} \end{aligned}

\operatorname{isc}(a,b) \stackrel{\operatorname{def}}{=} \operatorname{iswrite}_{\operatorname{locs}(b)}(a) \wedge \operatorname{sc}(a,b) \wedge \nexists c. \operatorname{sc}(a,c) \wedge \operatorname{sc}(c,b) \wedge \operatorname{iswrite}_{\operatorname{locs}(b)}(c)

Figure 3. Axioms satisfied by consistent C11 executions, Consistent (\mathcal{A}, lab, sb, rf, mo, sc).

violates CoherentRR

violates CoherentWR

violates CoherentRW

```

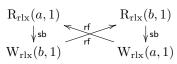

**Figure 4.** Sample executions violating coherency conditions (Batty et al. 2011).

**Consistent Executions** According to the C11 model, an execution is consistent, Consistent( $\mathcal{A}$ , lab, sb, rf, mo, sc), if all of the properties shown in Figure 3 hold.

(IrreflexiveHB) The happens-before order, hb, must be irreflexive: an action cannot happen before itself.

(ConsistentMO) All write actions on an atomic location  $\ell$  must be totally ordered by mo, and be consistently ordered by hb (restricted to the location  $\ell$ ).

(ConsistentSC) The sc relation must be a total order and include both hb and mo restricted to SC actions. This in effect means that SC actions are globally synchronized.

(ConsistentRFdom) The reads-from map, rf, is defined for those read (or RMW) actions for which the execution contains an earlier write (or RMW) to the same location.

(ConsistentRF) Each entry in the reads-from map, rf, should map a read to an earlier or concurrent write to the same location and with the same value.

(ConsistentRFna) Further, if a read reads from a write and either the read or write are non-atomic, then the write must have happened before the read. Batty et al. (2011) also require the write to be *visible*: i.e. not to have been overwritten by another write that happened before the read. This extra condition is unnecessary, as it follows from CoherentWR.

(RestrSCReads) SC reads are further restricted to read only from the immediately preceding SC write to the same location in sc order or from a non-SC write that has not happened before that immediately preceding SC write.

(CoherentRR,CoherentWR,CoherentRW) Next, we have three per-location coherence properties relating mo, hb, and rf. These properties require that mo never contradicts hb or the observed read order, and that rf never reads values that have been overwritten by more recent actions that happened before the read. These coherence properties are depicted in Figure 4.

(AtomicRMW) Each read-modify-write action should execute atomically: it should read from the immediately preceding write in mo.

(ConsistentAlloc) Finally, the same location cannot be allocated twice by different allocation actions.<sup>2</sup>

**Remark** Our model differs in a few minor ways from that of Batty et al. (2011, 2012). First, we have incorporated the C standard's "additional synchronized with" (asw) relation in sb rather than in sw, because it describes synchronization induced by control flow rather than by data flow.

Second, our sw-relation also relates acquire reads with release writes (whenever the read returns a value written by or after the release write), even if the two actions belong

$$\begin{array}{c} \mathbf{let}\;a=\mathbf{alloc}()\;\mathbf{in}\\ \mathbf{let}\;c=\mathbf{alloc}()\;\mathbf{in}\\ [c]_{\mathrm{rlx}}:=0;\\ \left(\begin{array}{c} [a]_{\mathrm{na}}:=7;\; \middle\|\; \mathbf{repeat}\; [c]_{\mathrm{acq}}\;\mathbf{end};\\ [c]_{\mathrm{rel}}:=1\; \middle\|\; [a]_{\mathrm{na}}:=[a]_{\mathrm{na}}+1 \end{array}\right) \end{array}$$

**Figure 5.** Message passing example showing transfer of ownership of the non-atomic location a.

to the same thread (and are thus sb-related), whereas Batty et al. (2012) do not add any sb-related actions to the sw-relation. Since relating such actions also by sw does not affect execution consistency, we do so for uniformity, which eases the definition of validity of Hoare triples in §7.

Finally, in the standard, the sb and sw relations are taken to be strict partial orders, corresponding to the transitive closure of our relations. Conversely, our sb relation can be defined in terms of the sb order from the C and C++ standards as follows,  $\mathsf{sb}_{\mathrm{our}} = \{(a,b) \in \mathsf{sb}_{\mathrm{std}} \cup \mathsf{asw}_{\mathrm{std}} \mid \not\exists c. \ (a,c) \in \mathsf{sb}_{\mathrm{std}} \cup \mathsf{asw}_{\mathrm{std}} \land (c,b) \in \mathsf{sb}_{\mathrm{std}} \cup \mathsf{asw}_{\mathrm{std}} \}.$  Again, we found the non-transitive versions slightly more convenient when defining the meaning of Hoare triples.

# 4. Relaxed Separation Logic

To motivate RSL, consider the message passing program shown in Figure 5. The thread on the left updates some data structure using non-atomic memory accesses (here, the location a), and then signals to other threads that the data structure has been updated by performing a release write to c. The thread on the right repeatedly performs acquire reads until it notices that  $[c] \neq 0$ . Then, it can conclude that the thread on the left has finished its work, and so may safely access the data structure without interfering with it.

This message passing idiom is correct (i.e., race-free) because whenever an acquire read sees the value written by a release write, the write "synchronizes with" the acquire read. Thus, as hb is transitive, any event that happened before the write (e.g., by being sequenced before it), also happens before the read. This, in turn, justifies the ownership transfer from the writing thread to the reading thread.

To model such ownership transfers, RSL extends the grammar of separation logic assertions, P, with three new assertion forms, Rel(e, Q), Acq(e, Q), and RMWAcq(e, Q), where Q ranges over functions from values to assertions. Formally, RSL assertions are given by following grammar:

$$\begin{array}{c} P,Q ::= \mathsf{false} \mid P \Rightarrow Q \mid \forall x. \; P \mid \mathsf{emp} \mid e \overset{k}{\mapsto} e' \mid P * Q \\ \mid \mathsf{Rel}(e,\mathcal{Q}) \mid \mathsf{Acq}(e,\mathcal{Q}) \mid \mathsf{RMWAcq}(e,\mathcal{Q}) \\ \mid \mathsf{Init}(e) \mid \mathsf{Uninit}(e) \end{array}$$

where k ranges over fractional permissions (Perm = (0,1], see Boyland 2003). We have the usual classical first order logic constructs (the three primitive ones and the derived: true,  $\land$ ,  $\lor$ ,  $\neg$ ,  $\exists$ ), the three assertions forms pertinent to separation logic (empty heap, a single memory cell with

<sup>&</sup>lt;sup>2</sup> This axiom suffices, because we do not support deallocation. Had we included deallocation, we would instead require there to be a deallocation actions between any two allocation actions of the same location. The formalized C11 model by Batty et al. (2011, 2012) does not model allocation.

Figure 6. Standard proof rules supported by RSL.

fractional permission k, and separating conjunction), and five new forms, which we will explain shortly.

RSL judgements are of the form  $\{P\}$  E  $\{y.$   $Q\}$ , where P and Q are assertions respectively denoting the precondition and the postcondition of the expression E. The postcondition, Q, also describes the return value of the expression E, which is bound by the variable y. In cases where the postcondition does not describe the return value, we often omit the y binder. With this setup, we support all the standard rules from Hoare and separation logic (see Figure 6) including the so-called 'structural' rules: the frame, consequence, disjunction, and existential rules.

Another generic rule we support is the RELAX rule below. Generally, when reasoning about a program E, we are always allowed to reason about a relaxation of the program  $E' \sqsubseteq E$ , which is identical to E except on the atomic access annotations, which may be weaker than those of E according to the partial order:  $\operatorname{rlx} \sqsubseteq \operatorname{rel} \sqsubseteq \operatorname{sc}, \operatorname{rlx} \sqsubseteq \operatorname{acq} \sqsubseteq \operatorname{sc}.$

$$\frac{\left\{P\right\}E'\left\{y.\,Q\right\}}{\left\{P\right\}E\left\{y.\,Q\right\}} \qquad \qquad \text{(RELAX)}$$

**Atomic Writes** We return to the treatment of atomic memory accesses and the new assertion forms. The first one,  $\text{Rel}(\ell,\mathcal{Q})$ , represents a permission to write any value v to location  $\ell$ , provided the assertion  $\mathcal{Q}(v)$  holds separately. Performing the write consumes the  $\mathcal{Q}(v)$  assertion so that it can be transferred to the reader(s).

$$\begin{cases} \mathcal{Q}(v) * \\ \mathsf{Rel}(\ell,\mathcal{Q}) \end{cases} [\ell]_{\mathrm{rel}} := v \begin{cases} \mathsf{Init}(\ell) * \\ \mathsf{Rel}(\ell,\mathcal{Q}) \end{cases}$$

(W-REL)

In order for the ownership transfer to be valid, the writer must synchronize with the reader(s), which means that the write must be at least of release kind (or stronger, namely SC). Besides the ownership transfer, the write also initializes the location  $\ell$ . Keeping track of initialized locations is necessary for subsequent proof rules. In the special case when no ownership transfer occurs (i.e., when P = emp), intuitively we can also use a relaxed write as in the following rule.

$$\left\{ \mathsf{Rel}(\ell, v, \mathsf{emp}) \right\} [\ell]_{\mathsf{rlx}} := v \left\{ \mathsf{Init}(\ell) \right\} \tag{W-RLX*}$$

In this rule, we used the following shorthand notation

$$Rel(\ell, v, P) \stackrel{\text{def}}{=} Rel(\ell, \lambda x. \text{ if } x = v \text{ then } P \text{ else false})$$

for representing the permission to write only the value v and release ownership of P (in this case emp). Intuitive though this rule is, it is unfortunately unsound in C11, as we will explain in Section 6, where we also show that we can restore its soundness by mildly strengthening the model.

In RSL, we allow multiple concurrent writes to the same atomic location by making the permission to perform an atomic write splittable as follows:

$$\begin{aligned} & \operatorname{Rel}(\ell, \mathcal{Q}_1) * \operatorname{Rel}(\ell, \mathcal{Q}_2) \\ & \iff \operatorname{Rel}(\ell, \lambda v. \ \mathcal{Q}_1(v) \lor \mathcal{Q}_2(v)) \end{aligned} \tag{REL-SPLIT}$$

Of course, programs that perform multiple concurrent writes to same location and transfer away ownership may leak memory, as some of the writes may be overwritten and thus never read. In this paper, however, we do not regard such memory leaks as an error. If desired, the programmer may explicitly count the number of allocations and deallocations in order to prove that the program has no memory leaks.

Similar to write permissions, the fact that a location has been initialized—captured by  $Init(\ell)$ —can be freely duplicated. Once a location is initialized, it remains initialized: it cannot be de-initialized.

$$\mathsf{Init}(\ell) \iff \mathsf{Init}(\ell) * \mathsf{Init}(\ell)$$

(INIT-SPLIT)

**Atomic Reads** The second assertion form,  $Acq(\ell, \mathcal{Q})$ , denotes a permission to perform an acquire read of location  $\ell$  and obtain ownership of  $\mathcal{Q}(v)$ , where v is the value read.

$$\frac{\forall x. \ \mathsf{precise}(\mathcal{Q}(x))}{\left\{ \begin{aligned} & \mathsf{Init}(\ell) * \\ & \mathsf{Acq}(\ell, \mathcal{Q}) \end{aligned} \right\} [\ell]_{\mathrm{acq}} \left\{ \begin{aligned} & v. \ \mathcal{Q}(v) * \\ & \mathsf{Acq}(\ell, \mathcal{Q}[v:=\mathsf{emp}]) \end{aligned} \right\}} \end{aligned} \tag{R-ACQ)}$$

The premise of the rule (that  $\mathcal Q$  should be precise) is a technical requirement that will be explained in Section 7 and may be ignored for the time being. As a precondition, we require not only the permission to perform an acquire read from  $\ell$ , but also the knowledge that the location has been initialized. The latter is needed because reading from uninitialized locations may return any arbitrary value and thus we cannot ensure that  $\mathcal Q(v)$  was ever established. When reading a value, we acquire  $\mathcal Q(v)$  and give up the permission to read the same value again with ownership transfer, because otherwise it would have been possible to acquire the same  $\mathcal Q(v)$  multiple times. Therefore, in the postcondition the assertion attached to the acquire predicate becomes

$$\mathcal{Q}[v{:=}\mathsf{emp}] \stackrel{\mathrm{def}}{=} \lambda y. \ \mathbf{if} \ y{=}v \ \mathbf{then} \ \mathsf{emp} \ \mathbf{else} \ \mathcal{Q}(y) \,.$$

This allows further reads of the same value, but consequent reads will simply not gain any ownership. At any point, it is also possible to do a relaxed read and acquire no ownership.

$$\left\{ \mathsf{Init}(\ell) * \mathsf{Acq}(\ell, \mathcal{Q}) \right\} [\ell]_{\mathrm{rlx}} \left\{ \mathsf{Acq}(\ell, \mathcal{Q}) \right\}$$

(R-RLX)

Note that this rule does not assert anything about the value read. A more useful rule is the following, which asserts that the value read must be one that may have been written.

Similar to W-RLX\*, this latter rule is not sound in C11, but is so in the strengthened model of Section 6.

In RSL, we permit multiple readers to read the value written by a single release write. Concretely, consider the scenario where thread A initializes two data structures and signals by a release write that it has finished its work. Then thread B can do an acquire read and notice that A has finished its initialization and then access the first data structure non-atomically. Likewise, thread C can do an acquire read and access the second data structure non-atomically. Such an execution does not have data races and should therefore be permitted. In terms of our program logic, this means that acquire read permissions should be splittable and joinable as follows:

$$\begin{array}{l} \mathsf{Acq}(\ell,\mathcal{Q}_1) * \mathsf{Acq}(\ell,\mathcal{Q}_2) \\ \iff \mathsf{Acq}(\ell,\lambda v.\ \mathcal{Q}_1(v) * \mathcal{Q}_2(v)) \end{array}$$

**Read-Modify-Write Instructions** The next new assertion form, RMWAcq $(\ell, \mathcal{Q})$ , is used in the following proof rule for atomic compare-and-swaps.

$$\begin{split} P &\Rightarrow \mathsf{Init}(\ell) * \mathsf{RMWAcq}(\ell, \mathcal{Q}) * \mathsf{true} \\ P * \mathcal{Q}(v) &\Rightarrow \mathsf{Rel}(\ell, \mathcal{Q}') * \mathcal{Q}'(v') * R[v/y] \\ X &\in \{\mathsf{rel}, \mathsf{rlx}\} \Rightarrow \mathcal{Q}(v) = \mathsf{emp} \\ X &\in \{\mathsf{acq}, \mathsf{rlx}\} \Rightarrow \mathcal{Q}'(v') = \mathsf{emp} \\ \frac{\left\{P\right\} \left[\ell\right]_Y \left\{y. \ y \neq v \Rightarrow R\right\}}{\left\{P\right\} \mathbf{CAS}_{X,Y}(\ell, v, v') \left\{y. \ R\right\}} \end{split} \tag{CAS*}$$

The rule has five premises. First, the precondition must ensure that we have permission to do a RMW-read from  $\ell$  and acquire ownership of  $\mathcal{Q}(v)$ . Second, we require the update performed by the successful CAS to be valid: that is, to have the necessary release permission, to satisfy  $\mathcal{Q}'(v')$ , the assertion that is to be transferred away, and to separately also satisfy the postcondition. As a precondition for this update, we get to assume not only that the initial precondition holds, but also that we have access to the state acquired by ownership transfer,  $\mathcal{Q}(v)$ .

The next two premises take the access modes into account, suitably restricting the ownership that can be acquired or released. If the successful  $\mathbf{CAS}$  is of release or relaxed kind, then it does not synchronize with the write whose value it read, so it should not acquire any ownership. This is ensured by demanding that  $\mathcal{Q}(v) = \mathsf{emp}$ . Symmetrically, if the successful  $\mathbf{CAS}$  is of acquire or relaxed kind, it does not synchronize with the reads seeing the value it produced, so it should not release any ownership. This is ensured by demanding that  $\mathcal{Q}'(v') = \mathsf{emp}$ .

Finally, we require that failed CASs also satisfy the postcondition, R, under the assumption that a value different from the expected one was read.

In its general form, the CAS\* rule is sound in the strengthened model of Section 6. In the standard model, it is sound only when  $X \in \{\text{rel\_acq}, \text{sc}\}.$

Unlike multiple normal reads, multiple successful CAS instructions cannot all read from (and therefore potentially synchronize with) the same write. This follows from the AtomicRMW axiom, which requires RMW actions to read from the immediately preceding write in mo-order. Therefore, it is sound to duplicate the RMW-acquire permission,

$$\mathsf{RMWAcq}(\ell, \mathcal{Q}) \\ \iff \mathsf{RMWAcq}(\ell, \mathcal{Q}) * \mathsf{RMWAcq}(\ell, \mathcal{Q})$$

(RMW-SPLIT)

because the semantics ensures that at most one process will effectively be able to use this permission at any given instant.

In order to be able to prove the last premise of the CAS\* rule, we also support the following rule, allowing us to carve out a plain acquire permission from an RMW-acquire one.

$$\frac{\forall v. \ \mathcal{Q}'(v) = \mathsf{emp} \lor \mathcal{Q}(v) = \mathcal{Q}'(v) = \mathsf{false}}{\mathsf{RMWAcq}(\ell, \mathcal{Q}) \iff \mathsf{RMWAcq}(\ell, \mathcal{Q}) * \mathsf{Acq}(\ell, \mathcal{Q}')}$$

(RMW-ACO-SPLIT)

The premise of RMW-ACQ-SPLIT ensures that the assertion that we have carved out for plain reads is empty, except perhaps for the values where  $\mathcal{Q}(v)$  is false, in which case  $\mathcal{Q}'(v)$  may also be false.

Allocation of Atomic Locations Whenever a new atomic location is allocated, the verifier is free to choose a suitable ownership assertion  $\mathcal Q$  and attach it to the newly allocated location, and moreover to choose whether the ownership of  $\mathcal Q$  will be acquired using plain reads or using successful  $\mathbf CAS$ s. We thus have the following two rules.

$$\begin{aligned} &\left\{\mathsf{emp}\right\} \mathbf{alloc}() \left\{\ell. \ \mathsf{Rel}(\ell, \mathcal{Q}) * \mathsf{Acq}(\ell, \mathcal{Q})\right\} \\ &\left\{\mathsf{emp}\right\} \mathbf{alloc}() \left\{\ell. \ \mathsf{Rel}(\ell, \mathcal{Q}) * \mathsf{RMWAcq}(\ell, \mathcal{Q})\right\} \end{aligned} \tag{A-R} \end{aligned}$$

Following the C standard, newly allocated locations are not initialized, and thus do not generate the  $\mathsf{Init}(\ell)$  permission required for reading them. To enable reading from these locations, the programmer must first initialize them by performing a plain write as we have already seen.

**Non-Atomic Locations** Finally, the rules for non-atomic accesses are exactly as in concurrent separation logic. Allocation returns an uninitialized new cell with full permission; writing requires full permission of a location (whether initialized or not), whereas reading works also with partial permission but requires the location to be initialized.

$$\begin{split} \left\{\mathsf{emp}\right\}\mathbf{alloc}()\left\{x.\,\mathsf{Uninit}(x)\right\} & \quad \text{(A-NA)} \\ \left\{\ell \overset{1}{\mapsto} \_ \lor \mathsf{Uninit}(\ell)\right\}[\ell]_{\mathrm{na}} &:= v\left\{\ell \overset{1}{\mapsto} v\right\} & \quad \text{(W-NA)} \\ \left\{\ell \overset{k}{\mapsto} v\right\}[\ell]_{\mathrm{na}}\left\{x.\,x = v \land \ell \overset{k}{\mapsto} v\right\} & \quad \text{(R-NA)} \end{split}$$

```

Let Q_J(v) \stackrel{\text{def}}{=} (v = 0 \land \text{emp}) \lor (v = 1 \land J)

Lock(x, J) \stackrel{\text{def}}{=} Rel(x, \mathcal{Q}_J) * RMWAcq(x, \mathcal{Q}_J) * Init(x)

new\_lock() \stackrel{\mathrm{def}}{=}

lock(x) \stackrel{\text{def}}{=}

\{Lock(x,J)\}

let x = alloc() in

repeat

\int J * \text{Rel}(x, \mathcal{Q}_J) *

\{Lock(x,J)\}

\bigcap \mathsf{RMWAcq}(x,\mathcal{Q}_J) \bigcap

spin(x);

[x]_{\text{rel}} := 1

\{Lock(x,J)\}

\{Lock(x,J)\}

\mathbf{CAS}_{\mathrm{acq,rlx}}(x,1,0)

\begin{cases} y.\ Lock(x,J)*\\ \left(y=1 \land J \lor \\ y=0 \land \mathsf{emp} \right) \end{cases}

unlock(x) \stackrel{\text{def}}{=}

\{J * Lock(x, J)\}

\begin{aligned} & \left\{ \sum_{i \in I} \operatorname{Loch}(x,J) \right\} \\ & \left[ x \right]_{\mathrm{rel}} := 1 \\ & \left\{ \operatorname{Init}(x) * \operatorname{Loch}(x,J) \right\} \\ & \left\{ \operatorname{Loch}(x,J) \right\} \end{aligned}

\{J * Lock(x, J)\}

\{Lock(x,J)\}

```

Figure 7. Verification of the lock module.

```

\begin{array}{l} \mathbf{Let} \ \mathcal{Q}(x) \stackrel{\mathrm{def}}{=} \mathbf{if} \ x = 0 \ \mathbf{then} \ \mathrm{emp} \ \mathrm{emp} \ \mathrm{let} \ a = \mathbf{alloc}() \ \mathbf{in} \\ \quad \left\{ \mathrm{Uninit}(a) \right\} \\ \quad \mathbf{let} \ c = \mathbf{alloc}() \ \mathbf{in} \\ \quad \left\{ \mathrm{Uninit}(a) * \operatorname{Rel}(c,\mathcal{Q}) * \operatorname{Acq}(c,\mathcal{Q}) \right\} \\ \quad \left[ c \right]_{\mathrm{rlx}} := 0; \\ \left\{ \mathrm{Uninit}(a) * \operatorname{Rel}(c,\mathcal{Q}) * \operatorname{Acq}(c,\mathcal{Q}) * \operatorname{Init}(c) \right\} \\ \left\{ \mathrm{Uninit}(a) * \operatorname{Rel}(c,\mathcal{Q}) * \operatorname{Acq}(c,\mathcal{Q}) * \operatorname{Init}(c) \right\} \\ \left\{ \mathrm{Ininit}(a) * \operatorname{Rel}(c,\mathcal{Q}) \right\} \\ \left[ a \right]_{\mathrm{na}} := 7 \\ \left\{ a \mapsto 7 * \operatorname{Rel}(c,\mathcal{Q}) \right\} \\ \left\{ c \right]_{\mathrm{rel}} := 1 \\ \left\{ \mathrm{Rel}(c,\mathcal{Q}) \right\} \\ \left\{ a \mapsto 8 * \operatorname{true} \right\} \\ \left\{ a \mapsto 8 * \operatorname{true} \right\} \end{aligned}

```

Figure 8. Verification of the message passing example.

These rules ensure that all accessed location have been allocated and there are no races on non-atomic memory locations, and moreover that only initialized locations are read.

## 5. Examples

We now illustrate RSL by proving simple race-free programs involving release-acquire synchronization patterns. Ownership transfer along those release-acquire synchronizations is necessary to prove them correct, that is, to show that they are memory safe and do not contain data races. To make the proof outlines more concise, we define the following shorthand notations.

$$\begin{split} \mathsf{Emp} &\stackrel{\mathrm{def}}{=} \lambda v. \ \mathsf{emp} \\ \mathsf{IAcq}(\ell, v, P) &\stackrel{\mathrm{def}}{=} \mathsf{Init}(\ell) * \mathsf{Acq}(\ell, \mathsf{Emp}[v := P]) \\ \mathsf{IRMWAcq}(\ell, v, P) &\stackrel{\mathrm{def}}{=} \mathsf{Init}(\ell) * \mathsf{RMWAcq}(\ell, \mathsf{Emp}[v := P]) \end{split}$$

Figure 7: Lock Module As our first example, we consider the lock module introduced in Figure 1. Here we show that

any invariant J may be attached to a lock so that we get the same specifications as in concurrent separation logic:

```

\left\{J\right\} new\_lock() \left\{x. \ Lock(x,J)\right\} \\ \left\{Lock(x,J)\right\} lock(x) \left\{J*Lock(x,J)\right\} \\ \left\{J*Lock(x,J)\right\} unlock(x) \left\{Lock(x,J)\right\} \\ Lock(x,J) \iff Lock(x,J)*Lock(x,J)

```

As expected, creating a lock requires the invariant J to hold initially and returns a token confirming that the lock exists and protects the invariant J. Acquiring the lock requires this token and obtains ownership of the invariant. Conversely, releasing the lock requires the invariant to hold and transfers it away. Finally, the token saying that x is a lock protecting resource J can be freely duplicated.

To derive this specification, we define the predicates:

$$\mathcal{Q}_J(v) \stackrel{\text{def}}{=} (v = 0 \land \text{emp}) \lor (v = 1 \land J)$$

$$Lock(x, J) \stackrel{\text{def}}{=} \text{Rel}(x, \mathcal{Q}_J) * \text{RMWAcq}(x, \mathcal{Q}_J) * \text{Init}(x)$$

The  $\mathcal{Q}_J(v)$  predicate describes the invariant associated with the location x implementing the lock. It assigns empty ownership when the lock is held  $(v=0 \land \text{emp})$ , and ownership of the invariant, J, when the lock is free  $(v=1 \land J)$ . The Lock(x,J) predicate contains permissions to access the lock by performing release-writes and acquire-RMWs. It also contains the knowledge that the lock is initialized.

In  $new\_lock()$ , we use the A-M and W-REL rules to initialize the location and transfer away the ownership of J. Similarly, in unlock(x), we use the W-REL to transfer away the ownership of J and then the INIT-SPLIT rule to remove the duplicate lnit(x) fact. In lock(x), we use the R-RLX rule for the relaxed optimistic read in the spin(x) loop, and then the CAS\* and the R-RLX\* rules to deal with the CAS. Finally, the fact that the Lock(x,J) predicate can be freely duplicated follows immediately from REL-SPLIT, RMW-SPLIT, and INIT-SPLIT.

*Figure 8: Message Passing* As our second example, we consider the message passing idiom of Figure 5. Here, by constructing a proof, we conclude that the program has no data races and moreover, when both threads terminate, we have [a] = 8. The proof illustrates the use of the Acq(-, -) predicate, and the rules A-NA, A-R, W-RLX\*, W-NA, W-REL, R-ACQ, and R-NA.

Figure 9: Partial Ownership Transfer Our next example is a variant of the message passing program we have just seen, where after the synchronization between the two threads, both threads read from a. This is valid because two concurrent read accesses do not count as a data race.

In order to verify this program, we use fractional permissions and transfer the partial ownership of the non-atomic location a from the first to the second thread. The first thread writes to a, and then performs a release write to x, giving

```

\left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3) * \operatorname{Rel}(lock, 1, \operatorname{emp}) * \operatorname{IRMWAcq}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel{1}{\mapsto} 3)\right\}   \left\{a \stackrel{1}{\mapsto} \_* \operatorname{Rel}(lock, 0, a \stackrel{1}{\mapsto} 2 \vee a \stackrel

```

Figure 10. Example illustrating the use of CAS to implement a lock.

**Figure 9.** Example illustrating fractional ownership and transfer thereof.

away the partial permission  $a \overset{0.6}{\mapsto} 2$  (using the W-REL rule). With its remaining  $a \overset{0.4}{\mapsto} 2$  permission, it then reads a using the R-NA rule. The second thread synchronizes with the write to x and gets the  $a \overset{0.6}{\mapsto} 2$  permission (using the R-ACQ rule), after which it reads a and also gets the value 2 (using the R-NA rule).

Figure 10: Transfer of Permission in Both Directions Our next example demonstrates the use of CAS directly to implement a simple mutual exclusion lock. (We could of course use the lock module verified previously, but we include this example in order to demonstrate the CAS\* rule again.) Here, for a change, we implement a non-blocking "tryLock" command using a conditional, rather than a blocking locking command using a loop.

The lock is implemented by a single location, lock, storing 0 if the lock is free and 1 if it is held. (This is opposite to the covention of the earlier lock module.) The lock protects a resource invariant describing the memory cell a. Initially, the first thread starts with the lock acquired and owning a: it establishes the resource invariant and releases the lock. The other two threads start without knowing that the lock was initially held; they both have the permission to write the value 1 to the lock without releasing any owner-

```

\begin{array}{c} \mathbf{let}\; a = \mathbf{alloc}()\; \mathbf{in}\; [a]_{\mathrm{rlx}} := 0;\\ \mathbf{let}\; b = \mathbf{alloc}()\; \mathbf{in}\; [b]_{\mathrm{rlx}} := 0;\\ \left(\mathbf{if}\; 1 = [a]_{\mathrm{rlx}}\; \mathbf{then}\right) \; \left\| \begin{array}{c} (\mathbf{if}\; 1 = [b]_{\mathrm{rlx}}\; \mathbf{then}\\ [a]_{\mathrm{rlx}} := 1 \end{array} \right) \end{array}

```

Figure 11. Program with a possible dependency cycle.

[Initialization actions not shown]

Figure 12. Execution exhibiting the dependency cycle.

ship, Rel(lock, 1, emp). By itself, this permission is pretty useless: the threads can do a blind relaxed-atomic write to lock setting its value to 1 (acquired) but without gaining any information. What makes this permission useful, is its combination with the other permission they have, namely to read the state of an unacquired lock with a CAS and get ownership of the resource invariant. Successfully performing the CAS enables them to later release the lock with the same resource invariant.

# 6. Dealing with Relaxed Memory Accesses

A serious deficiency of the C11 memory model is that it allows "out of thin air" reads, as illustrated by the program in Figure 11, adapted from Batty et al. (2013).

In this program, two locations are initialized with the value 0, and then two threads are forked, each writing 1 to the one location provided the other already has the value 1. Intuitively, one would expect that the writes would never be executed, but actually the C11 concurrency model permits this outcome. The questionable execution, depicted in Figure 12, is consistent as the two reads can get the value 1 by reading from the corresponding conditional stores.

This counterintuitive behaviour is extremely problematic for formal reasoning as it inhibits even the simplest form

$$\begin{aligned} & \mathbf{let} \ a = \mathbf{alloc}() \ \mathbf{in} \ [a]_{\rm rlx} := 0; \\ & \mathbf{let} \ b = \mathbf{alloc}() \ \mathbf{in} \ [b]_{\rm rlx} := 1; \\ & \left( [b]_{\rm rlx} := [a]_{\rm rlx} \, \middle\| \, [a]_{\rm rlx} := [b]_{\rm rlx} \right); \\ & \mathbf{if} \ [a]_{\rm rlx} < 20 \ \mathbf{then} \ \mathbf{print} \ [a]_{\rm rlx} \end{aligned}$$

**Figure 13.** Program showing that range analysis is unsound under C11.

of thread-local reasoning, that of non-relational conjunctive invariants (i.e., invariants where each conjunct describes a property of only one variable). Intuitively, in the previous program, one would expect the invariant

$$[a]_{\rm rlx} = 0 \land [b]_{\rm rlx} = 0$$

to hold throughout the parallel composition since it holds initially and is preserved by every 'reachable' atomic statement of the program, arguing that the conditional stores are not reachable because the conditions are unsatisfiable according to the invariant. This kind of reasoning is performed by standard compiler optimizations such as "sparse conditional constant propagation" (Wegman and Zadeck 1991).

Note that with the W-RLX\* and R-RLX\* rules, we can easily prove that if we were to read [a] at the end of the program, we would get 0. (To do so, pick  $\mathcal{Q} := (\lambda x. \ x = 0)$  in the allocation rule for both locations.) This shows that these two rules are unsound under C11.

Observe that the same problematic execution remains consistent even if we strengthen either the relaxed reads to acquire/SC reads or (exclusively) the relaxed writes to release/SC writes. To make this execution inconsistent, we have to strengthen both the reads and the writes except at most one access. This means that even adding one of the W-RLX\* and R-RLX\* rules is unsound.

Global Range Analysis A concrete optimization that is unsound under C11 is global range analysis. Consider the program in Figure 13. An optimizing compiler may argue that the test  $[a]_{\rm rlx} < 20$  will always succeed because [a] and [b] store either 0 or 1, and therefore replace the conditional expression by the then branch. Somewhat surprisingly, under C11, this transformation introduces new behaviour and is therefore unsound. Because of the causal dependency cycle, the  $[a]_{\rm rlx}$  read can return any arbitrary value. Therefore, the transformed program can print any arbitrary value, while the original one could only print values less than 20.

A Crude Fix to the Model Since even this very basic reasoning is unsound for relaxed accesses, we decided to strengthen the C11 concurrency model with the following axiom stating that  $hb \cup rf$  must be acyclic (i.e., its transitive closure must be irreflexive).

$$\mbox{acyclic(hb} \cup \{(\mbox{rf}(a), a) \mid a \in \mathcal{A}\}) \quad (\mbox{StrongAcyclicHB})$$

where  $\mbox{acyclic}(R) \stackrel{\mbox{\scriptsize def}}{=} \nexists x \in \mathcal{A}. \ R^+(x, x).$

$$\begin{split} & \mathbf{let} \ a = \mathbf{alloc}() \ \mathbf{in} \ [a]_{\mathrm{rlx}} := 0; \\ & \mathbf{let} \ b = \mathbf{alloc}() \ \mathbf{in} \ [b]_{\mathrm{rlx}} := 0; \\ & \left( \mathbf{let} \ x = [a]_{\mathrm{rlx}} \ \mathbf{in} \right) \ \left\| \begin{array}{c} (\mathbf{let} \ y = [b]_{\mathrm{rlx}} \ \mathbf{in} \\ [a]_{\mathrm{rlx}} := 1 \end{array} \right) \end{split}$$

Figure 14. Program without a dependency cycle.

With this additional axiom, we can also show the soundness of the "starred" rules for relaxed memory accesses presented in the previous section. In contrast, the soundness of the other rules does not depend on this axiom.

Notice that when adding this strong acyclicity condition, we can drop the strictly weaker IrreflexiveHB axiom, as well as the  $\neg hb(b,a)$  conjunct from the ConsistentRF axiom. We can further drop the slightly awkward ConsistentRFna axiom, and still have the soundness proof go through, because all the proof really needs to know is that the write precedes the read in some well-founded order. In the absence of causal cycles, this order need not be hb: we can instead take it to be hb  $\cup$  rf.

Simple though our proposed fix might seem, it is not perfect. Alas, the StrongAcyclicHB consistency axiom precludes the reordering of independent instructions, a transformation that compilers and processors with out-of-order execution units frequently perform. To illustrate the problem, consider the program in Figure 14, a slight variant of the program in Figure 11, where the writes to [b] and [a]are now independent of the earlier reads from [a] and [b] respectively. The problem is that when operating at the level of single executions, one cannot distinguish whether the hb∪rf cycle in the execution shown in Figure 12 constitutes a dependency cycle or not. If the execution comes from the program in Figure 11, the cycle should clearly be outlawed, but if it comes from the program of Figure 14, the cycle is harmless and should be allowed. Distinguishing these two cases is not easy and seems to require a radical change to the C11 model. Clearly, this lies beyond the scope of this paper.

## 7. Semantics and Soundness

In this section, we define the semantics of assertions and Hoare triples, and prove that our logic is sound with respect to the C11 memory model.

#### 7.1 Semantics of Assertions

To define the meaning of separation logic assertions, we need an underlying separation algebra, i.e. a commutative partial monoid. To interpret the Acq and Rel assertions, our model of heaps will have to store assertions, which in turn represent sets of heaps. If we naively write down the domain equation, we will get an equation of the form,

$$\mathsf{Heap}_{\mathrm{spec}} \overset{?}{\cong} \mathsf{Loc} \rightharpoonup \left( ... + \left( ... \times \mathbb{P}(\mathsf{Heap}_{\mathrm{spec}}) \right) \right),$$

which does not have a solution in Set. Therefore, we either have to move to a more advanced category such as bounded

$$\mathcal{Q}_1 \oplus_{\operatorname{acq}}^{b_1,b_2} \mathcal{Q}_2 \stackrel{\operatorname{def}}{=} \begin{cases} \mathcal{Q}_1 & \text{if } b_1 \wedge b_2 \text{ and } \mathcal{Q}_1 = \mathcal{Q}_2 \\ \lambda v. \ \mathcal{Q}_1(v) * \mathcal{Q}_2(v) & \text{if } (\neg b_1 \vee \neg b_2) \text{ and } \operatorname{adef}(b_1,\mathcal{Q}_1,b_2,\mathcal{Q}_2) \\ \operatorname{undef} & \text{if } \neg \operatorname{adef}(b_1,\mathcal{Q}_1,b_2,\mathcal{Q}_2) \end{cases} \qquad \begin{array}{c} \operatorname{rval}(b,\mathcal{Q}) \stackrel{\operatorname{def}}{=} \operatorname{if } b \operatorname{then } \mathcal{Q} \operatorname{else } \lambda v. \operatorname{emp} \\ \operatorname{adef}(b_1,\mathcal{Q}_1,b_2,\mathcal{Q}_2) \stackrel{\operatorname{def}}{=} \\ \forall v. \ \operatorname{rval}(b_2,\mathcal{Q}_1)(v) = \operatorname{rval}(b_1,\mathcal{Q}_2)(v) \\ \vee \mathcal{Q}_1(v) = \mathcal{Q}_2(v) = \operatorname{false} \end{cases}$$

$$h_1 \oplus h_2 \stackrel{\operatorname{def}}{=} \lambda \ell. \begin{cases} h_1(\ell) & \operatorname{if } \ell \in \operatorname{dom}(h_1) \setminus \operatorname{dom}(h_2) \\ h_2(\ell) & \operatorname{if } \ell \in \operatorname{dom}(h_2) \setminus \operatorname{dom}(h_1) \\ \operatorname{NA}[v,k_1+k_2] & \operatorname{if } h_i(\ell) = \operatorname{NA}[v,k_i] \operatorname{for } i = 1,2 \operatorname{and } k_1+k_2 \leq 1 \\ \operatorname{Atom}[\lambda v. \ \mathcal{R}_1(v) \vee \mathcal{R}_2(v), \mathcal{Q}_1 \oplus_{\operatorname{acq}}^{b_1,b_2} \mathcal{Q}_2, b_1 \vee b_2, b_1' \vee b_2'] & \operatorname{if } h_i(\ell) = \operatorname{Atom}[\mathcal{R}_i,\mathcal{Q}_i,b_i,b_i'] \operatorname{for } i = 1,2 \\ \operatorname{undef} & \operatorname{otherwise} \end{cases}$$

$$h_1 \oplus h_2 \stackrel{\operatorname{def}}{=} \begin{cases} h_1 \oplus' h_2 & \operatorname{if } \operatorname{dom}(h_1 \oplus' h_2) = \operatorname{dom}(h_1) \cup \operatorname{dom}(h_2) \\ \operatorname{undef} & \operatorname{otherwise} \end{cases}$$

**Figure 15.** Definition of heap composition,  $h_1 \oplus h_2$ .

ultrametric spaces (Birkedal et al. 2010), or change the equation to avoid the problematic recursion.

Here, for simplicity, we do the latter and cut the cycle by storing syntactic assertions, Assn, instead of semantic assertions,  $\mathbb{P}(\mathsf{Heap}_{\mathrm{spec}})$ , within heaps. Simply storing syntactic assertions is, however, insufficient because we want the heap model to form a separation algebra and to support the conversions rules REL-SPLIT and ACQ-SPLIT. To allow these conversions, we therefore have to store syntactic assertions up to associativity and commutativity of \* and  $\vee$  and their units. Furthermore, to support RMW-ACQ-SPLIT, we also need to equate false \* false and false. Formally, we define  $\sim$  to be the smallest equivalence relation on syntactic assertions, equating the following assertions:

- (S1)  $\forall P, Q \in \mathsf{Assn.}\ P * Q \sim Q * P$ ,

- (S2)  $\forall P, Q, R \in \mathsf{Assn.}\ P*(Q*R) \sim (P*Q)*R$ ,

- (S3)  $\forall P \in \mathsf{Assn.}\ P * \mathsf{emp} \sim P$ ,

- (S4) false \* false  $\sim$  false,

- (S5)  $\forall P, Q \in \mathsf{Assn.}\ P \lor Q \sim Q \lor P$ ,

- (S6)  $\forall P, Q, R \in \mathsf{Assn.} \ P \lor (Q \lor R) \sim (P \lor Q) \lor R$ , and

- (S7)  $\forall P \in \mathsf{Assn.} (P \vee \mathsf{false}) \sim (P \vee P) \sim P$ .

where, for convenience, we have also included idempotence for disjunction. The model of heaps, Heap<sub>spec</sub>, therefore is:

$$\begin{split} \mathsf{Perm} &\stackrel{\mathrm{def}}{=} (0,1] & \mathbb{B} \stackrel{\mathrm{def}}{=} \{\mathsf{true}, \mathsf{false}\} \\ \mathcal{M} &\stackrel{\mathrm{def}}{=} \mathsf{Val} \to \mathsf{Assn}/{\sim} \\ \mathsf{Heap}_{\mathrm{spec}} &\stackrel{\mathrm{def}}{=} \mathsf{Loc} \rightharpoonup \begin{pmatrix} \mathsf{NA}[\mathbb{U} + (\mathsf{Val} \times \mathsf{Perm})] \\ + \mathsf{Atom}[\mathcal{M} \times \mathcal{M} \times \mathbb{B} \times \mathbb{B}] \end{pmatrix} \end{split}$$

Each allocated location is either non-atomic or atomic. Non-atomic locations can either be uninitialized (represented by special symbol  $\mathbb{U}$ ) or contain a value and a permission. Atomic locations contain two maps from values to syntactic assertions modulo  $\sim$  and two Boolean flags. The two maps represent the release and the acquire maps used to interpret the three assertion forms pertinent to RSL:  $\text{Rel}(\ell, \mathcal{Q})$ ,  $\text{Acq}(\ell, \mathcal{Q})$ , and  $\text{RMWAcq}(\ell, \mathcal{Q})$ , with the first Boolean flag indicating whether the second map acts as a plain acquire

map or as an RMW-acquire map. The second Boolean flag records whether the location has been initialized or not.

Figure 15 defines the composition of two *logically disjoint* heaps,  $h_1 \oplus h_2$ . Note that two logically disjoint heaps can share some locations, provided that they store compatible information about them. For non-atomic locations, they should be initialized and have compatible permissions (i.e., whose sum does not exceed the full permission, 1). For atomic locations, the two heaps must contain compatible acquire maps, represented by the predicate  $\mathbf{adef}(b_1, \mathcal{Q}_1, b_2, \mathcal{Q}_2)$ . This predicate is somewhat complex because acquire maps represent plain acquire or RMW-acquire permissions depending on the relevant Boolean flag. The cases are:

```

(Case b_1 \wedge b_2) we must have \mathcal{Q}_1 = \mathcal{Q}_2;

(Case b_1 \wedge \neg b_2) we require that for all v, either \mathcal{Q}_2(v) = \text{emp or } \mathcal{Q}_1(v) = \mathcal{Q}_2(v) = \text{false};

(Case \neg b_1 \wedge b_2) symmetrically to the previous case; and (Case \neg b_1 \wedge \neg b_2) no conditions.

```

Given these definitions, we can show that  $(\mathsf{Heap}_{\mathrm{spec}}, \oplus, \emptyset)$  forms a separation algebra, which in turn means that it is a good model for separation logic assertions.

**Lemma 1.** (Heap<sub>spec</sub>,  $\oplus$ ,  $\emptyset$ ) forms a separation algebra. That is,  $\oplus$  is associative, commutative, and has  $\emptyset$  as its identity element.

In the proof of this lemma, property S4 is required to show associativity; replacing S4 with the more general property  $\forall P \in \mathsf{Assn.}\ P * \mathsf{false} \sim \mathsf{false}\ \mathsf{breaks}\ \mathsf{associativity}.$

We remark that in contrast to most models for separation logic, our  $\oplus$  is not cancellative. For example, consider the heap  $h_{\rm I}=\{\ell\mapsto {\sf Atom}[{\sf False},{\sf Emp},{\sf false},{\sf true}]\}$ . Clearly,  $h_{\rm I}\neq\emptyset$  and yet  $h_{\rm I}\oplus h_{\rm I}=h_{\rm I}=h_{\rm I}\oplus\emptyset$ . In practice, the lack of cancellativity does not affect reasoning about RSL assertions. It also does not mean that the heap model contains 'junk' information. Indeed, the heap  $h_{\rm I}$  is used to model the assertion  ${\sf Init}(\ell)$ , and we want  $h_{\rm I}\oplus h_{\rm I}=h_{\rm I}$  to validate INIT-SPLIT.

#### **Definition 1** (Assertion Semantics).

```

\begin{split} \text{Let} \, & \big[ - \big] : \mathsf{Assn} \to \mathbb{P} \big( \mathsf{Heap}_{\mathrm{spec}} \big) \, \mathit{be} \colon \\ & \big[ \mathsf{false} \big] \stackrel{\mathrm{def}}{=} \emptyset \\ & \big[ P \Rightarrow Q \big] \stackrel{\mathrm{def}}{=} \{ h \mid h \in [\![P]\!] \implies h \in [\![Q]\!] \} \\ & \big[ \forall x. \, P \big] \stackrel{\mathrm{def}}{=} \{ h \mid \forall v. \, h \in [\![P[\![v/x]\!]\!] \} \\ & \big[ \mathsf{emp} \big] \stackrel{\mathrm{def}}{=} \{ \emptyset \} \\ & \big[ P * Q \big] \stackrel{\mathrm{def}}{=} \{ h_1 \oplus h_2 \mid h_1 \in [\![P]\!] \land h_2 \in [\![Q]\!] \} \\ & \big[ [\![Uninit(\ell)]\!] \stackrel{\mathrm{def}}{=} \{ \{ \ell \mapsto \mathsf{NA}[\mathbb{U}] \} \} \\ & \big[ \ell \stackrel{k}{\mapsto} v \big] \stackrel{\mathrm{def}}{=} \{ \{ \ell \mapsto \mathsf{NA}[v,k] \} \} \\ & \big[ [\![Init(\ell)]\!] \stackrel{\mathrm{def}}{=} \{ \{ \ell \mapsto \mathsf{Atom}[\mathsf{False}, \mathsf{Emp}, \mathsf{false}, \mathsf{true}] \} \} \\ & \big[ [\![Rel(\ell,Q)]\!] \stackrel{\mathrm{def}}{=} \{ \{ \ell \mapsto \mathsf{Atom}[\mathsf{False}, \mathcal{Q}, \mathsf{false}, \mathsf{false}] \} \} \\ & \big[ [\![RMWAcq(\ell,Q)]\!] \stackrel{\mathrm{def}}{=} \{ \{ \ell \mapsto \mathsf{Atom}[\mathsf{False}, \mathcal{Q}, \mathsf{true}, \mathsf{false}] \} \} \\ & \big[ \mathsf{RMWAcq}(\ell,Q) \big] \stackrel{\mathrm{def}}{=} \{ \{ \ell \mapsto \mathsf{Atom}[\mathsf{False}, \mathcal{Q}, \mathsf{true}, \mathsf{false}] \} \} \\ & where \, \mathsf{False} \stackrel{\mathrm{def}}{=} \lambda v. \, \mathsf{false} \, \mathit{and} \, \mathsf{Emp} \stackrel{\mathrm{def}}{=} \lambda v. \, \mathsf{emp}. \end{split}

```

Figure 16. Definition of the semantics of assertions.

Equipped with specification heaps,  $\mathsf{Heap}_{\mathrm{spec}}$ , we proceed to the semantics of assertions. These are given as a function  $\llbracket - \rrbracket : \mathsf{Assn} \to \mathbb{P}(\mathsf{Heap}_{\mathrm{spec}})$  in Figure 16.

A basic property of the assertion semantics, that justifies treating stored assertions up to  $\sim$ , is that  $\sim$ -related assertions have the same semantics.

**Lemma 2.** If

$$P \sim Q$$

, then  $[\![P]\!] = [\![Q]\!]$ .

Moreover, we can easily show that our model validates the logical entailments of Section 4.

**Lemma 3.** *The properties* REL-SPLIT, ACQ-SPLIT, RMW-SPLIT, RMW-ACQ-SPLIT, *and* INIT-SPLIT *hold universally.*

Finally, we say that an assertion is *precise* if and only if it uniquely determines a subheap where it holds. The definition is standard (O'Hearn 2007), but due of the lack of cancellativity of  $\oplus$  we require both the heaps satisfying the assertion to be equal  $(h_1 = h'_1)$  as well as their remainders  $(h_2 = h'_2)$ . If  $\oplus$  were cancellative, then either of the equalities would suffice as it would imply the other.

**Definition 2** (Precision). An assertion is precise, denoted precise(P), if and only if for all  $h_1$ ,  $h'_1$ ,  $h_2$ ,  $h'_2$ , if  $h_1 \in \llbracket P \rrbracket$  and  $h_2 \in \llbracket P \rrbracket$  and  $h_1 \oplus h'_1 = h_2 \oplus h'_2 \neq \text{undef}$ , then  $h_1 = h'_1$  and  $h_2 = h'_2$ .

## 7.2 Semantics of Hoare triples

We move on to the meaning of RSL triples,  $\{P\}$  E  $\{y.$   $Q\}$ . To handle both models—the C11 standard one and the strengthened one of Section 6—we parametrize the definitions of the semantics of triples and all auxiliary definitions with respect to the model. For notational simplicity, however, we will present the definitions only for the strengthened model and we will note in text any differences for the standard C11 model.

Given an execution  $\mathcal{X} = \langle \mathcal{A}, \mathsf{lab}, \mathsf{sb}, \mathsf{rf}, \mathsf{mo}, \mathsf{sc} \rangle$ , we define the helper functions:  $\mathsf{SBin}_{\mathcal{X}}(a)$ ,  $\mathsf{SBout}_{\mathcal{X}}(a)$ ,  $\mathsf{SWin}_{\mathcal{X}}(a)$ ,

and  $\mathsf{SWout}_{\mathcal{X}}(a)$ , to get the set of sb/sw incoming/outgoing edges of an action  $a \in \mathcal{A}$ . Given also a set of actions,  $V \subseteq \mathcal{A}$ , we denote the set of its hb and rf predecessors as  $\mathsf{Pre}_{\mathcal{X}}(V)$ .

$$\mathsf{Pre}_{\mathcal{X}}(V) \stackrel{\mathrm{def}}{=} \{ a \mid \exists b \in V. \ \mathsf{hb}(a,b) \lor a = \mathsf{rf}(b) \}$$

This definition is very useful because we will generally be considering sets of actions V that are prefix-closed, namely  $\operatorname{Pre}_{\mathcal{X}}(V) \subseteq V$ , and we will be growing such sets by adding one action at a time while maintaining prefix-closure. Doing so is always possible for consistent executions because of the StrongAcyclicHB axiom. In the standard C11 model, we have to resort to a stronger definition of  $\operatorname{Pre}_{\mathcal{X}}(V)$  that includes only the hb edges, not arbitrary rf edges as well.

$$\mathsf{Pre}^{\mathsf{standard\_C11}}_{\mathcal{X}}(V) \stackrel{\mathrm{def}}{=} \{a \mid \exists b \in V.\ \mathsf{hb}(a,b)\}$$

To define the meaning of RSL triples, we will generally be annotating hb-edges with appropriate heaps. When doing so, however, it will be important to distinguish between happens-before edges that occur because of an sb-edge and those that occur because of an sw-edge. We therefore introduce the following definition that tags them accordingly.

**Definition 3** (Tagged Happens Before). *Given an execution*  $\mathcal{X}$ , *let* thb<sub> $\mathcal{X}$ </sub> *be a tagged union of* sb<sub> $\mathcal{X}$ </sub> *and* sw<sub> $\mathcal{X}$ </sub>, *constructed as follows*

$$\mathsf{thb}_{\mathcal{X}} \stackrel{\mathrm{def}}{=} \left\{ (\text{``sb"}, a, b) \mid (a, b) \in \mathsf{sb}_{\mathcal{X}} \right\} \\ \cup \left\{ (\text{``sw"}, a, b) \mid (a, b) \in \mathsf{sw}_{\mathcal{X}} \right\}$$

For a program expression, E, we denote  $\mathcal{C}[\![E]\!]$  as the set of its *consistent contextual executions*. These executions are obtained by plugging in an execution of E in some arbitrary execution context, such that the whole execution is consistent, as follows.

$$\begin{split} \mathcal{C} \llbracket E \rrbracket &\stackrel{\mathrm{def}}{=} \{ \ \langle res, \mathcal{A}_{\mathrm{ctx}}, \mathcal{A}_{\mathrm{prg}}, \mathcal{X}, fst, lst \rangle \ | \ \exists \mathsf{lab}_{\mathrm{ctx}}, \mathsf{lab}_{\mathrm{prg}}. \\ \exists \mathsf{sb}. \ \exists \mathsf{sb}_{\mathrm{prg}} = \mathsf{sb} \cap (\mathcal{A}_{\mathrm{prg}} \times \mathcal{A}_{\mathrm{prg}}). \\ \mathcal{X} &= \langle \mathcal{A}_{\mathrm{ctx}} \uplus \mathcal{A}_{\mathrm{prg}}, \mathsf{lab}_{\mathrm{ctx}} \cup \mathsf{lab}_{\mathrm{prg}}, \mathsf{sb}, \_, \_, \_ \rangle \\ & \wedge \langle res, \mathcal{A}_{\mathrm{prg}}, \mathsf{lab}_{\mathrm{prg}}, \mathsf{sb}_{\mathrm{prg}}, fst, lst \rangle \in \llbracket E \rrbracket \\ & \wedge (\exists ! a. \ \mathsf{sb}(a, fst)) \wedge (\exists ! b. \ \mathsf{sb}(lst, b)) \\ & \wedge \mathsf{Consistent}(\mathcal{X}) \ \} \end{split}$$

In the definition of C[E], we require that (1) the part of the execution corresponding to the expression matches its semantics, (2) fst has a unique sb-predecessor, (3) lst has a unique sb-successor, and (4) the entire execution is consistent. The requirements about the unique predecessor of fst and the unique successor of lst will be used for selecting unique edges responsible for carrying the expression's precondition and postcondition.

To define the meaning of RSL triples, we will annotate the thb-edges of consistent contextual executions with heaps. We will call such functions,  $hmap: \mathsf{thb}_{\mathcal{X}} \rightharpoonup \mathsf{Heap}_{\mathtt{spec}}$ ,

**Definition 4** (Local annotation validity). Given an execution,  $\mathcal{X} = \langle \mathcal{A}, \mathsf{lab}, \mathsf{sb}, \mathsf{rf}, \mathsf{mo}, \mathsf{sc} \rangle$ , a heap map,  $hmap : \mathsf{thb}_{\mathcal{X}} \rightharpoonup \mathsf{Heap}_{\mathrm{spec}}$ , and a set of actions  $V \subseteq \mathcal{A}$ , the predicate  $\mathsf{Valid}(hmap, V)$  holds if and only if for all actions  $a \in V$ , there exist  $\ell, v, \mathcal{Q}, \mathcal{Q}', \mathcal{Q}'', \mathcal{Z}, h_1, h_1', h_2, h_{\mathrm{F}}, h_{\mathrm{sink}}$  such that

```

/ lab(a) = skip